# Sub1G SoC HW3181 数据手册

- □产品简介

- ☑ 数据手册

- □产品规格

上海东软载波微电子有限公司

2021年10月8日

版权所有©上海东软载波微电子有限公司

## 产品订购信息

| Part NO.   | 工作电压       | FLASH | SRAM | I/O | Timer                 | RTC | UART | SPI | I2C | ADC         | 封装类型  |

|------------|------------|-------|------|-----|-----------------------|-----|------|-----|-----|-------------|-------|

| HW3181FHNQ | 2.2V ~3.6V | 36KB  | 8KB  | 32  | 16-bit×4,<br>32-bit×1 | 1   | 3    | 1   | 1   | 12-bit×15ch | QFN48 |

地 址:中国上海市徐汇区古美路 1515 号凤凰园 12 号楼 3 楼

E-mail: support@essemi.com 电 话: +86-21-60910333 传 真: +86-21-60914991

网 址: http://www.essemi.com

## 版权所有©

## 上海东软载波微电子有限公司

本资料内容为上海东软载波微电子有限公司在现有数据资料基础上慎重且力求准确无误编制而成,本资料中所记载的实例以正确的使用方法和标准操作为前提,使用方在应用该等实例时请充分考虑外部诸条件,上海东软载波微电子有限公司不担保或确认该等实例在使用方的适用性、适当性或完整性,上海东软载波微电子有限公司亦不对使用方因使用本资料所有内容而可能或已经带来的风险或后果承担任何法律责任。基于使本资料的内容更加完善等原因,上海东软载波微电子有限公司保留未经预告的修改权。使用方如需获得最新的产品信息,请随时用上述联系方式与上海东软载波微电子有限公司联系。

V1.5 2/352

## 修订历史

| 版本   | 修改日期       | 更改概要                                                                                                                                              |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0 | 2018-10-12 | 初版发布                                                                                                                                              |

| V1.1 | 2019-1-14  | 1. 更新 BOR 1.7V 和 2.1V 档位的复位电压上限范围为 2.35V。 2. 在"深度睡眠模式"章节,添加进睡眠模式前清所有中断挂起标志位的备注。 3. 更新 Logo。                                                       |

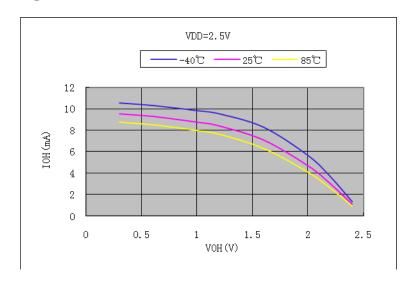

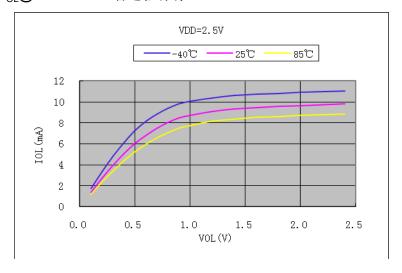

| V1.2 | 2019-4-22  | 1. 更新 MCU 的 IO 端口 VDD=2.5V 条件下的输出特性曲线;<br>2. 更新功耗参数表中,关于 ADC 模块和 VREF 模块的功耗参数;<br>3. 修改 BOR 模块特性表中的最低档位的电压范围上限为2.38V;<br>4. 更新 CLKFLT 旁路控制位的使用说明。 |

| V1.3 | 2020-3-5   | 1. 11.1 节频点设置更新<br>2. HOPSPACE 寄存器说明更新                                                                                                            |

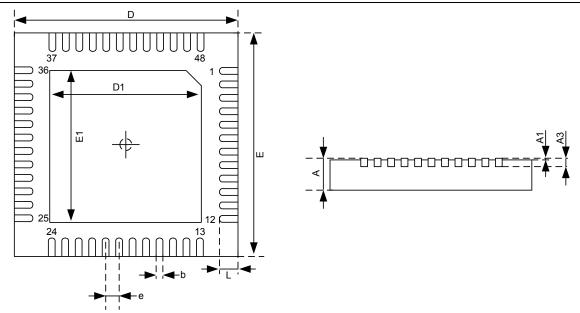

| V1.4 | 2021-1-6   | 1. 更新 QFN48 的 POD 图及参数; 2. 删除管脚分配图章节中关于 PA6 端口的应用限制备注; 3. 在寄存器 IAP_ADDR 的描述中添加不建议通过 IAP 操作 FLASH INFO 区的备注; 4. 增强"芯片配置字"章节中对 CFG_DEBUG 位的描述。      |

| V1.5 | 2021-10-8  | 更新公司地址。                                                                                                                                           |

## 目 录

#### 内容目录 第 1 章 芯片简介.......17 1.1 1.2 管脚分配图.......22 1.3 1.3.1 管脚说明.......23 1.4 1.4.1 1.4.2 1.4.3 1.4.4 第 2 章 系统控制及操作特性.......27 2. 1 2. 1. 1 2.1.2 2. 2 系统电源.......28 2 2 1 结构框图 28 2.2.2 2.3 概述......28 2.3.1 2.3.2 2.3.3 2.3.4 2.3.5 2. 4 低电压监测(LVD) 32 2.4.1 概述.......32 2.4.2 2. 5 系统低功耗操作模式......34 2.5.1 2.5.2 2.5.3 2.5.4 睡眠模式的唤醒.......35 2. 5. 5 睡眠模式的唤醒时间.......35 2.5.6

2.5.7

2. 6. 1 2. 6. 2

2.6.3

2.6.4

2.6.5

2.6

2.7

4/352

|   | 2. 7. 1  | 中断和异常                         | 54 |

|---|----------|-------------------------------|----|

|   | 2.7.2    | 中断和异常向量的分配                    | 55 |

|   | 2.7.3    | 中断向量表的重映射                     | 56 |

|   | 2.7.4    | 特殊功能寄存器                       | 56 |

|   | 2. 8     | 系统控制块(SCB)                    | 65 |

|   | 2. 8. 1  | 概述                            | 65 |

|   | 2. 8. 2  | 特殊功能寄存器                       | 65 |

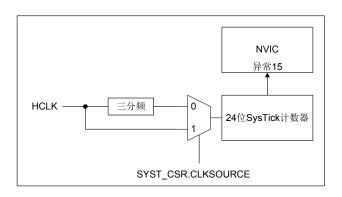

|   | 2. 9     | 系统定时器(SYSTICK)                | 69 |

|   | 2. 9. 1  | 概述                            | 69 |

|   | 2. 9. 2  | 特殊功能寄存器                       | 70 |

|   | 2. 10    | 配置字软件控制                       | 72 |

|   | 2. 11    | 定时器(T16N/T32N)同步启动关停控制        | 73 |

|   | 2. 11. 1 | 概述                            | 73 |

|   | 2. 11. 2 | 特殊功能寄存器                       | 73 |

| 第 | 3 章      | 存储器资源                         | 75 |

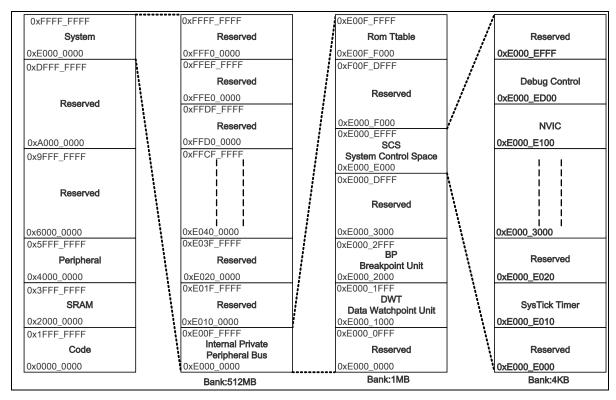

|   | 3. 1     | 内部存储器地址映射                     | 75 |

|   | 3. 2     | FLASH 存储器                     | 75 |

|   | 3. 2. 1  | 信息区 FLASH                     | 75 |

|   | 3. 2. 2  | 程序区 FLASH                     | 78 |

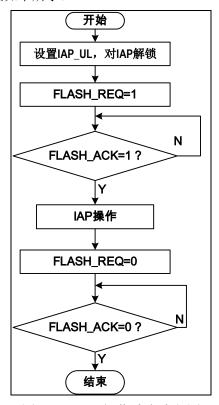

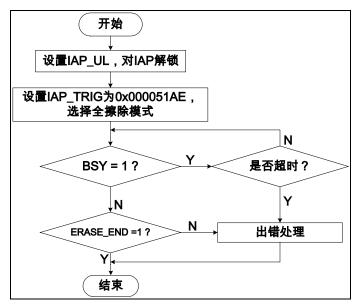

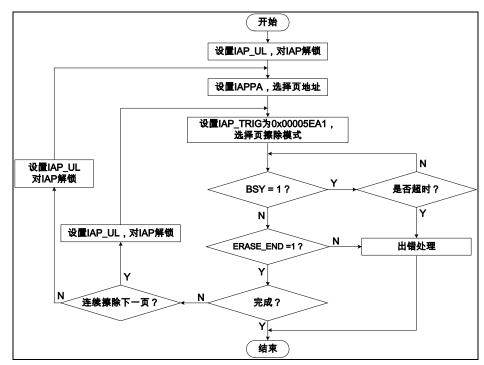

|   | 3. 2. 3  | 自编程操作(IAP)                    | 78 |

|   | 3. 2. 4  | 特殊功能寄存器                       | 82 |

|   | 3. 3     | 数据存储器(SRAM)                   | 86 |

|   | 3. 3. 1  | SRAM 地址映射                     | 86 |

|   | 3. 3. 2  | SRAM 位带扩展                     | 86 |

|   | 3. 4     | 外设寄存器                         | 87 |

|   | 3. 4. 1  | 外设寄存器映射                       | 87 |

|   | 3. 4. 2  | 外设寄存器位带扩展                     | 87 |

|   | 3. 4. 3  | 系统控制单元(SCU)寄存器列表              | 88 |

|   | 3. 4. 4  | GPIO 寄存器列表                    | 88 |

|   | 3. 4. 5  | IAP 寄存器列表                     | 90 |

|   | 3. 4. 6  | ADC 寄存器列表                     | 90 |

|   | 3. 4. 7  | RTC 寄存器列表                     | 90 |

|   | 3. 4. 8  | WDT 寄存器列表                     |    |

|   | 3. 4. 9  | T16N0/T16N1/T16N2/T16N3 寄存器列表 | 91 |

|   | 3. 4. 10 | T32N0 寄存器列表                   | 92 |

|   | 3. 4. 11 | UART0/UART1 寄存器列表             |    |

|   | 3. 4. 12 | EUART0 寄存器列表                  | 93 |

|   | 3. 4. 13 | SPI0/ SPI1 寄存器列表              |    |

|   | 3. 4. 14 | I2C0 寄存器列表                    |    |

|   | 3. 5     | 内核寄存器                         |    |

|   | 3. 5. 1  | 系统定时器(SYSTICK)寄存器列表           |    |

|   | 3. 5. 2  | 中断控制器(NVIC)寄存器列表              |    |

|   | 3. 5. 3  | 系统控制块(SCB)寄存器列表               | 95 |

| 第 | 4 章      | 输入输出端口(GPIO)                  | 96 |

|   | 4. 1     | 概述                        | 96  |

|---|----------|---------------------------|-----|

|   | 4. 2     | 外部端口中断                    | 97  |

|   | 4. 3     | 外部按键中断                    | 98  |

|   | 4. 4     | Buzz 输出                   | 99  |

|   | 4. 5     | 特殊功能寄存器                   | 100 |

| 第 | 5 章      | 外设                        | 125 |

|   | 5. 1     | 定时器/计数器                   | 125 |

|   | 5. 1. 1  | 16 位定时器/计数器 T16N          | 125 |

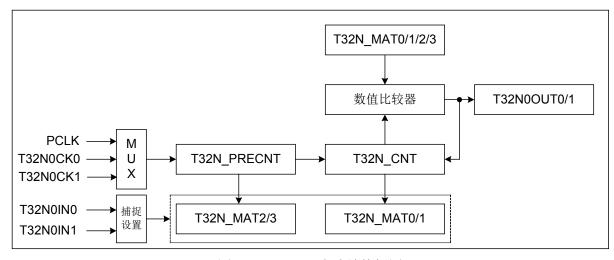

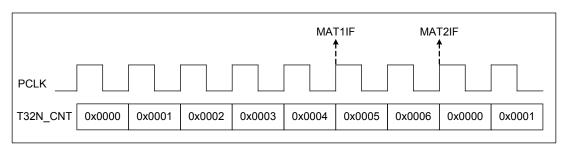

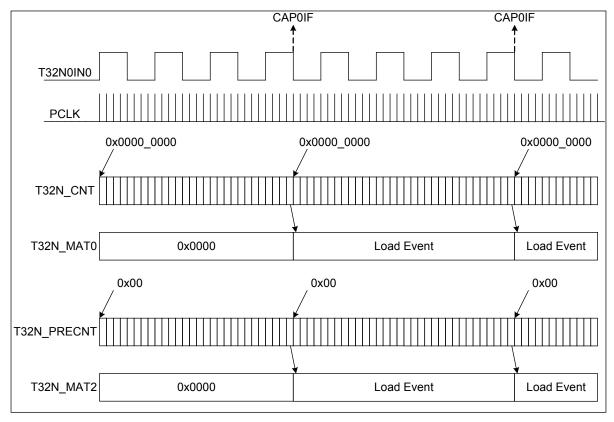

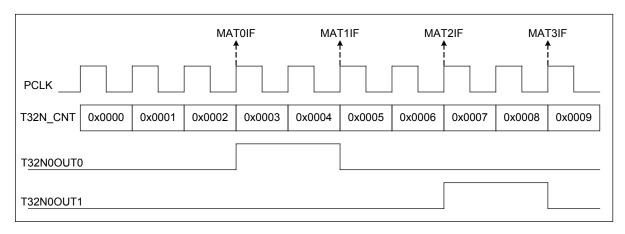

|   | 5. 1. 2  | 32 位定时器/计数器 T32N(T32N0)   | 145 |

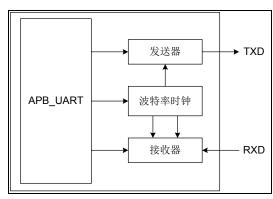

|   | 5. 2     | 通用异步接收/发送器(UART0/ UART1)  | 157 |

|   | 5. 2. 1  | 概述                        | 157 |

|   | 5. 2. 2  | 结构框图                      | 157 |

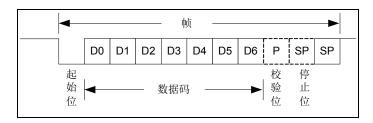

|   | 5. 2. 3  | UART 数据格式                 | 158 |

|   | 5. 2. 4  | UART 异步发送器                | 158 |

|   | 5. 2. 5  | UART 异步接收器                | 161 |

|   | 5. 2. 6  | UART 发送调制功能               | 163 |

|   | 5. 2. 7  | UART 红外唤醒功能               | 163 |

|   | 5. 2. 8  | UART 端口极性                 | 163 |

|   | 5. 2. 9  | UART 自动波特率检测              | 163 |

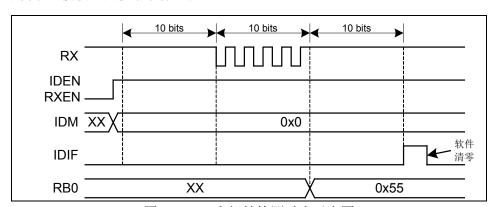

|   | 5. 2. 10 | UART 空闲帧检测                | 165 |

|   | 5. 2. 11 | UART 发送暂停和接收暂停            | 165 |

|   | 5. 2. 12 | 特殊功能寄存器                   | 166 |

|   | 5. 2. 13 | UART 应用说明                 | 182 |

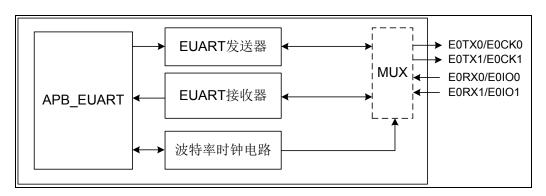

|   | 5. 3     | 增强型通用异步接收/发送器(EUARTO)     | 183 |

|   | 5. 3. 1  | 概述                        | 183 |

|   | 5. 3. 2  | 结构框图                      | 183 |

|   | 5. 3. 3  | EUART 端口复用                | 183 |

|   | 5. 3. 4  | 普通 UART 通讯模式              | 184 |

|   | 5. 3. 5  | 7816 通讯模式的异步接收器和发送器       | 184 |

|   | 5. 3. 6  | 7816 通讯模式的数据格式            | 185 |

|   | 5. 3. 7  | 7816 通讯模式的自动重发功能          | 185 |

|   | 5. 3. 8  | 7816 通讯模式的自动重收功能          | 186 |

|   | 5. 3. 9  | 特殊功能寄存器                   | 186 |

|   | 5. 3. 10 | EUART 应用说明                | 197 |

|   | 5. 4     | SPI 同步串口通讯控制器(SPI0 /SPI1) | 198 |

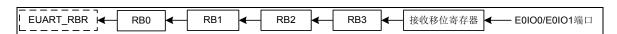

|   | 5. 4. 1  | 概述                        | 198 |

|   | 5. 4. 2  | 结构框图                      | 198 |

|   | 5. 4. 3  | SPI 通讯模式                  | 198 |

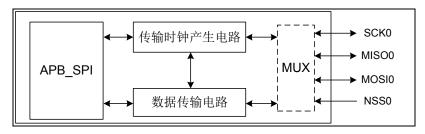

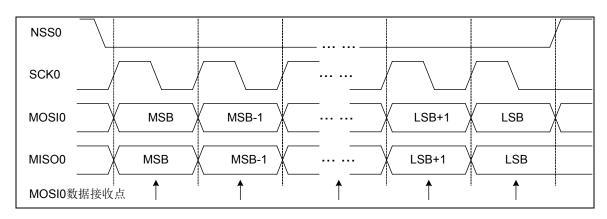

|   | 5. 4. 4  | SPI 数据格式                  | 198 |

|   | 5. 4. 5  | SPI 帧位宽                   | 200 |

|   | 5. 4. 6  | SPI 同步发送器                 | 200 |

|   | 5. 4. 7  | SPI 同步接收器                 | 201 |

|   | 5. 4. 8  | SPI 通讯控制                  | 202 |

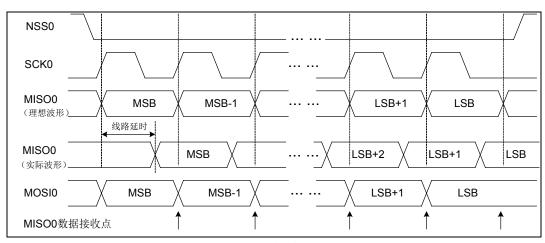

|   | 5. 4. 9  | SPI 延迟接收功能                | 202 |

|          | 5. 4. 10 | SPI 数据帧发送间隔功能       | 203 |

|----------|----------|---------------------|-----|

|          | 5. 4. 11 | 特殊功能寄存器             | 203 |

|          | 5. 4. 12 | SPI 应用说明            | 209 |

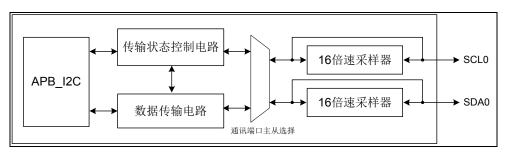

|          | 5. 5     | I2C 总线串口通讯控制器(I2C0) | 210 |

|          | 5. 5. 1  | 概述                  | 210 |

|          | 5. 5. 2  | 结构框图                | 210 |

|          | 5. 5. 3  | I2C 总线基本原理          | 210 |

|          | 5. 5. 4  | I2C 通讯端口配置          | 212 |

|          | 5. 5. 5  | I2C 时基定时器与 16 倍速采样器 | 213 |

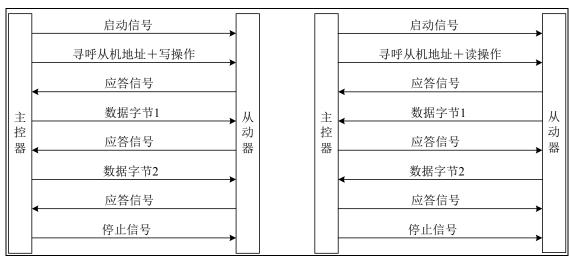

|          | 5. 5. 6  | I2C 通讯发送器           | 214 |

|          | 5. 5. 7  | I2C 通讯接收器           | 215 |

|          | 5. 5. 8  | I2C 通讯控制            | 215 |

|          | 5. 5. 9  | 特殊功能寄存器             | 218 |

|          | 5. 5. 10 | I2C 应用说明            | 226 |

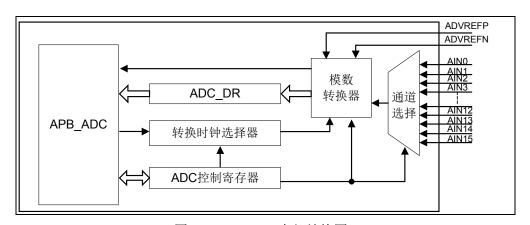

|          | 5. 6     | 模数转换器(ADC)          | 227 |

|          | 5. 6. 1  | 概述                  | 227 |

|          | 5. 6. 2  | 结构框图                | 227 |

|          | 5. 6. 3  | ADC 基本配置            | 227 |

|          | 5. 6. 4  | ADC 高精度参考电压         | 227 |

|          | 5. 6. 5  | ADC 数据转换            | 227 |

|          | 5. 6. 6  | 自动转换比较功能            |     |

|          | 5. 6. 7  | 特殊功能寄存器             |     |

|          | 5. 7     | 实时时钟(RTC)           |     |

|          | 5. 7. 1  | 概述                  |     |

|          | 5. 7. 2  | RTC 写保护             |     |

|          | 5. 7. 3  | 时间日期设置              |     |

|          | 5. 7. 4  | RTC 中断源             |     |

|          | 5. 7. 5  | RTC 计时功能            |     |

|          | 5. 7. 6  | 特殊功能寄存器             |     |

|          | 5. 8     | 看门狗定时器(WDT)         |     |

|          | 5. 8. 1  | 概述                  |     |

| ***      | 5. 8. 2  | 特殊功能寄存器             |     |

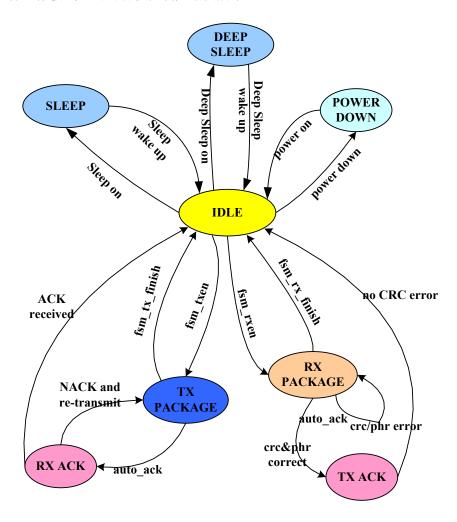

| 第        | 6 章      | RF 收发器一芯片状态控制       |     |

|          | 6. 1     | POWER DOWN          |     |

|          | 6. 2     | DEEP SLEEP          |     |

|          | 6. 3     | SLEEP (RC)          |     |

|          | 6. 4     | IDLE                |     |

|          | 6. 5     | TX                  |     |

|          | 6. 6     | # LUV + 174 × 271   |     |

| <i>_</i> | 6. 7     | 芯片状态切换说明            |     |

| 弟        | 7 章      | RF 收发器一帧结构          |     |

|          | 7. 1     | 增强型帧结构              |     |

| <i>p</i> | 7. 2     | 直接 FIFO 帧结构         |     |

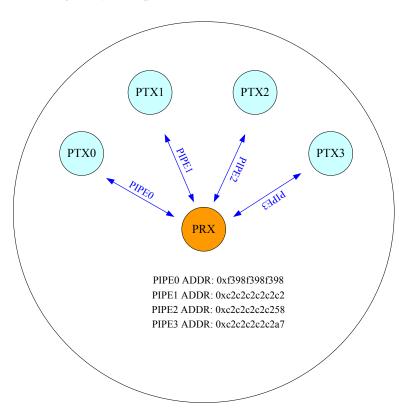

| 弟        | 8 章      | RF 收发器一多 PIPE 逻辑通道  | 258 |

| 第 | 9 章      | RF 收发器一自动 ACK 与 ART | 259 |

|---|----------|---------------------|-----|

| 第 | 10 章     | RF 收发器一数据与控制接口      | 260 |

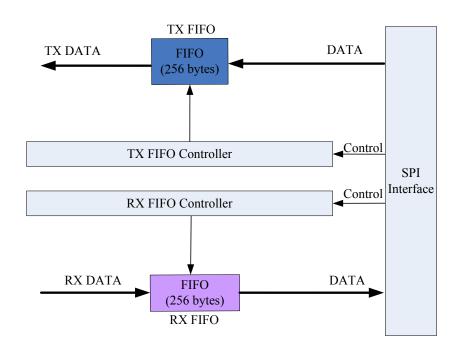

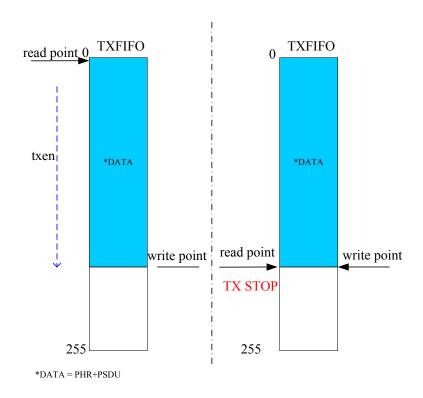

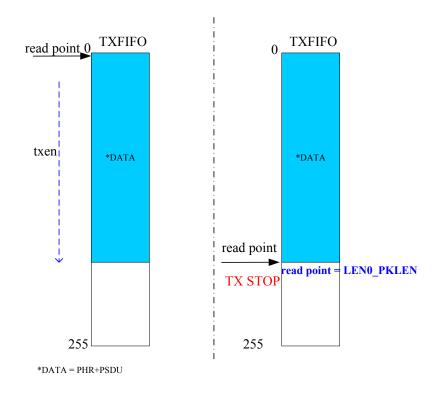

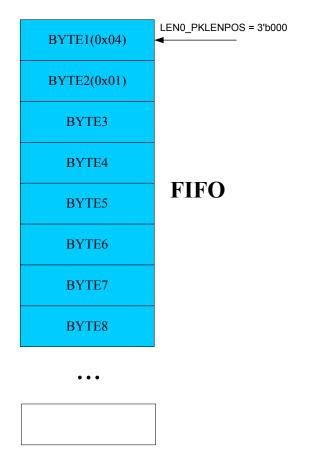

|   | 10. 1    | FIFO                | 260 |

|   | 10. 1. 1 | FIFO 指针             | 260 |

|   | 10. 1. 2 | FIFO 操作说明           | 261 |

|   | 10. 2    | 中断                  | 263 |

|   | 10. 2. 1 | 增强型帧结构中断            | 265 |

|   | 10. 2. 2 | 直接 FIFO 帧结构中断       | 268 |

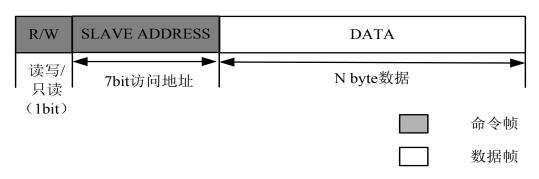

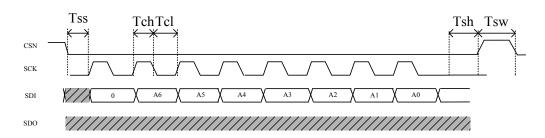

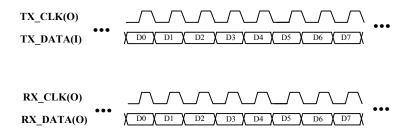

|   | 10. 3    | SPI 通信接口            | 269 |

|   | 10. 3. 1 | SPI 帧格式             | 269 |

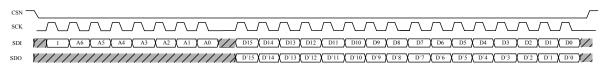

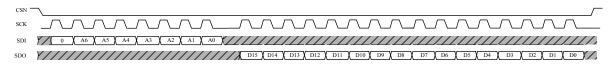

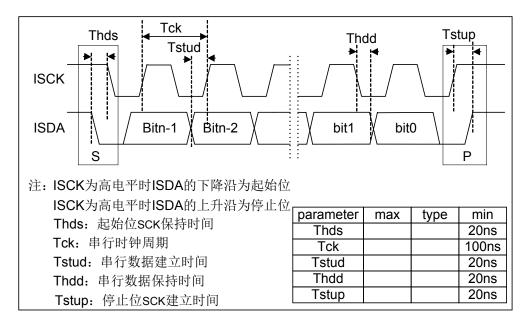

|   | 10. 3. 2 | 寄存器访问时序             | 270 |

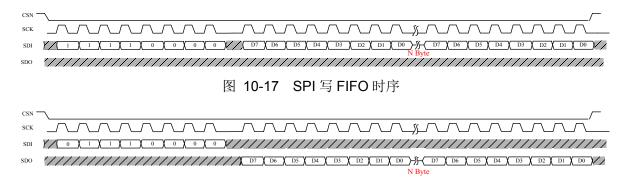

|   | 10. 3. 3 | FIFO 访问时序           | 270 |

|   | 10. 3. 4 | SPI 时序参数            | 270 |

|   | 10. 4    | GPIO 配置             | 271 |

| 第 | 11 章     | RF 收发器一频点与数据传输参数设置  | 272 |

|   | 11. 1    | 频点设置                | 272 |

|   | 11. 1. 1 | 频点默认设置模式            | 272 |

|   | 11. 1. 2 | 频点直接设置模式            | 273 |

|   | 11. 1. 3 | 跳频接收模式              | 273 |

|   | 11. 2    | 数据传输参数设置            | 274 |

|   | 11. 2. 1 | 数据速率设置              | 274 |

|   | 11. 2. 2 | 发送调制特性设置            | 274 |

|   | 11. 2. 3 | 发送功率设置              | 274 |

|   | 11. 2. 4 | 接收滤波器带宽设置           | 275 |

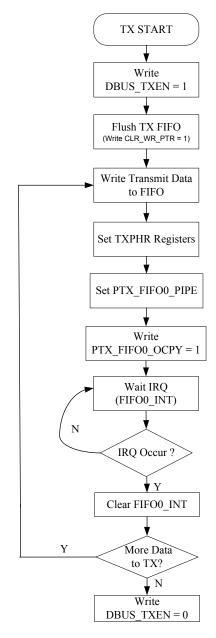

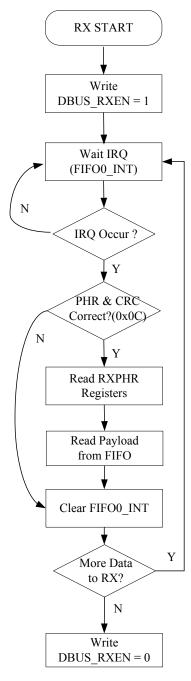

| 第 | 12 章     | RF 收发器一收发操作流程       | 276 |

|   | 12. 1    | 增强型帧结构收发流程          | 276 |

|   | 12. 2    | 直接 FIFO 帧结构收发流程     | 278 |

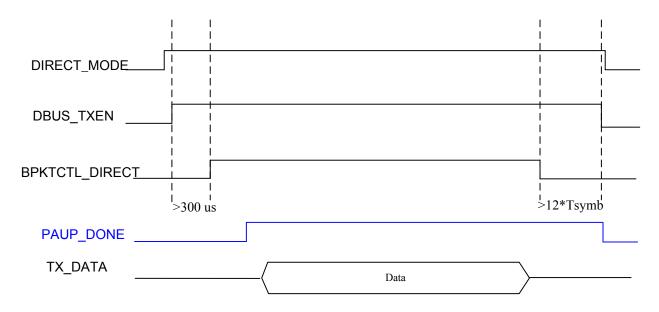

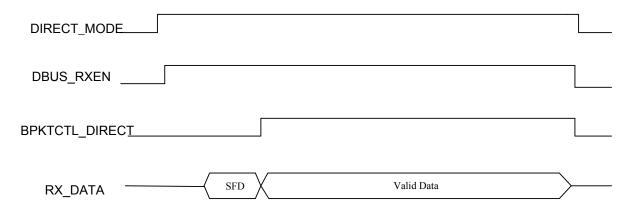

|   | 12. 3    | 直接收发 DIRECT 模式      | 280 |

|   | 12. 4    | 连续发送模式              | 282 |

| 第 | 13 章     | RF 收发器一唤醒           | 283 |

|   | 13. 1    | Wake-up Timer 唤醒    | 283 |

|   | 13. 2    | GPIO 外部中断唤醒         | 283 |

| 第 | 14 章     | RF 收发器—RC 校准        | 284 |

|   | 14. 1    | 软件校准                | 284 |

|   | 14. 2    | 硬件自动校准              | 284 |

| 第 | 15 章     | RF 收发器—异常状态的检测及复位   | 285 |

|   | 15. 1    | 芯片异常状态检测            | 285 |

|   | 15. 2    | 寄存器与 FIFO 校验功能      | 285 |

|   | 15. 3    | 芯片复位                | 285 |

| 第 | 16 章     | RF 收发器一其它功能与设置      | 286 |

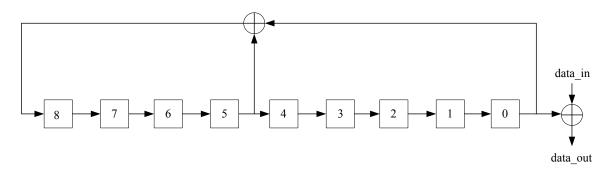

|   | 16. 1    | 白化与 CRC             | 286 |

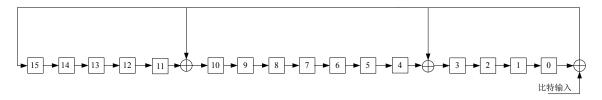

|   | 16. 2    | FEC                 | 286 |

|   | 16. 3    | 数据编码                | 287 |

|   | 16. 4    | RSSI                | 287 |

|   | 16. 5     | 载波检测(Carrier Detect)              | 287 |

|---|-----------|-----------------------------------|-----|

|   | 16. 6     | AFC 及晶振的校准功能                      | 287 |

|   | 16. 7     | 有效/无效前导检测                         | 288 |

|   | 16. 8     | 有效/无效 SFD 检测                      | 288 |

|   | 16. 9     | 低功耗接收模式                           | 288 |

| 第 | 17 章      | RF 收发器一寄存器                        | 289 |

|   | 17. 1     | 寄存器列表                             | 289 |

|   | 17. 2     | 寄存器说明                             | 291 |

| 第 | 18 章      | 封装尺寸图                             | 320 |

|   | 18. 1     | 封装尺寸图                             | 320 |

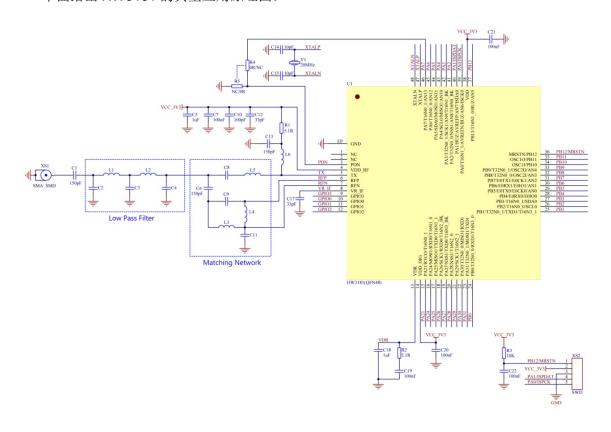

| 第 | 19 章      | 典型应用原理图                           | 321 |

|   | 19. 1     | 典型应用原理图                           | 321 |

|   | 19. 2     | 设计应用注意事项                          | 322 |

| 第 | 20 章      | 电气特性                              | 323 |

|   | 20. 1     | MCU 电气特性                          | 323 |

|   | 20. 1. 1  | 最大标称值                             |     |

|   | 20. 1. 2  | MCU 工作条件                          |     |

|   | 20. 1. 3  | MCU 功能模块工作电压范围                    | 323 |

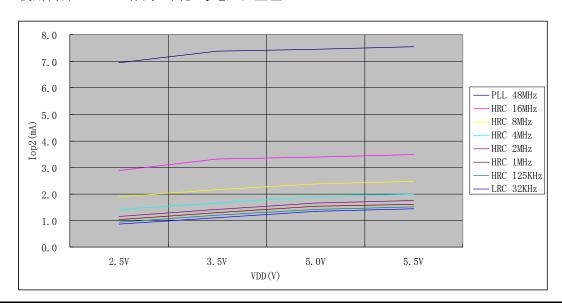

|   | 20. 1. 4  | MCU 功耗参数                          | 323 |

|   | 20. 1. 5  | MCU 功能模块功耗特性参数表                   | 325 |

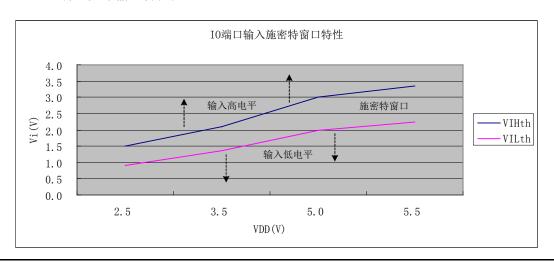

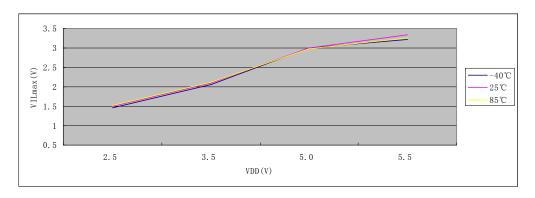

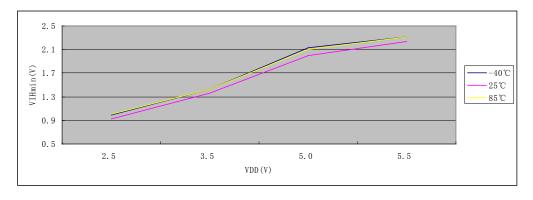

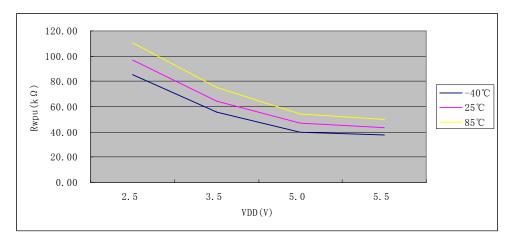

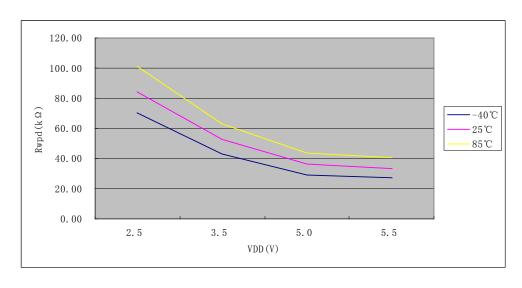

|   | 20. 1. 6  | MCU 输入输出端口特性                      | 326 |

|   | 20. 1. 7  | 系统时钟规格                            | 327 |

|   | 20. 1. 8  | ADC 模块特性                          | 327 |

|   | 20. 1. 9  | 内部时钟源特性                           | 329 |

|   | 20. 1. 10 | PLL 锁相环特性                         | 329 |

|   | 20. 1. 11 | BOR 模块特性                          |     |

|   | 20. 1. 12 |                                   |     |

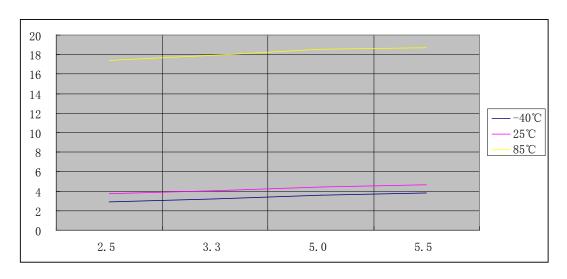

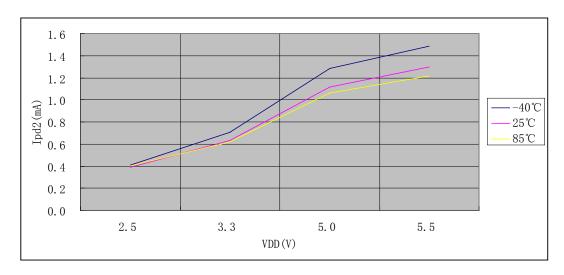

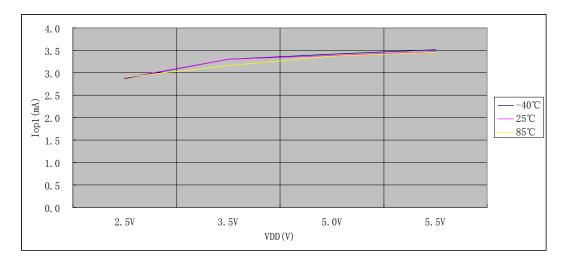

|   | 20. 2     | MCU 参数特性图                         |     |

|   | 20. 2. 1  |                                   |     |

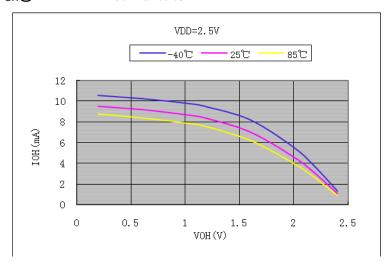

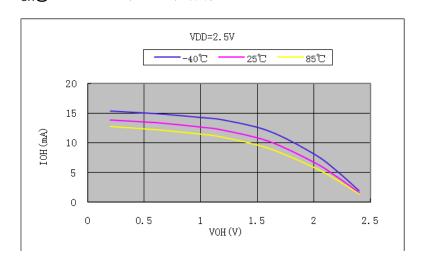

|   | 20. 2. 2  | 芯片 IO 端口输入特性                      |     |

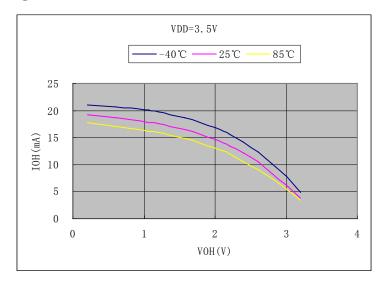

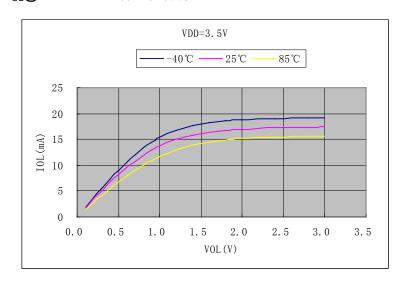

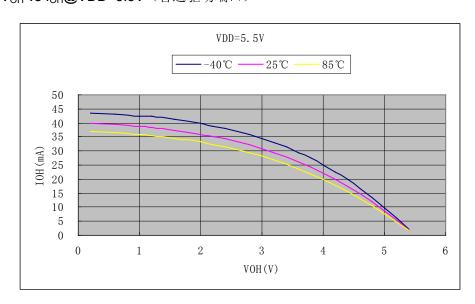

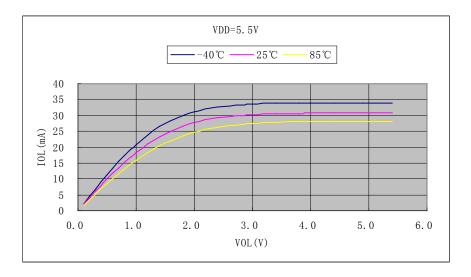

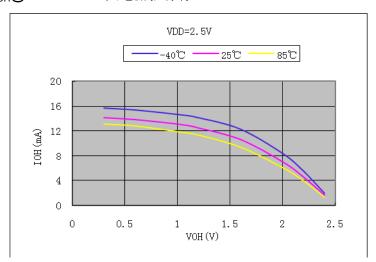

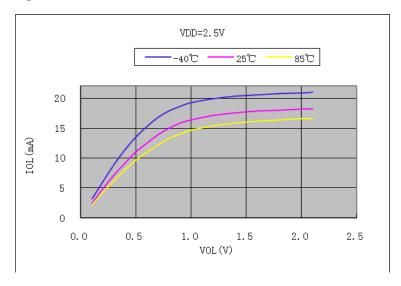

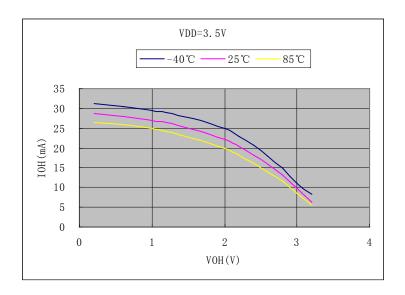

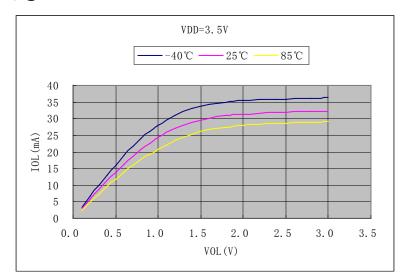

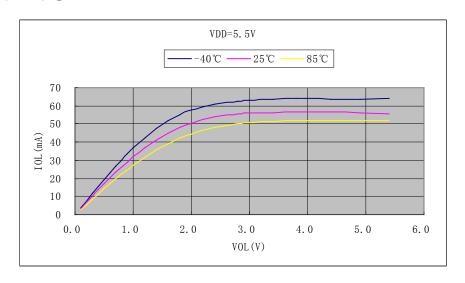

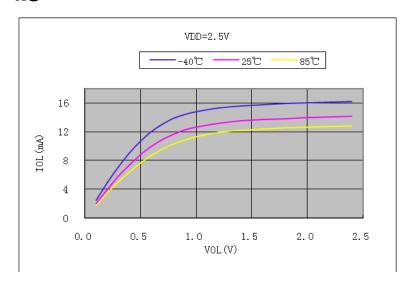

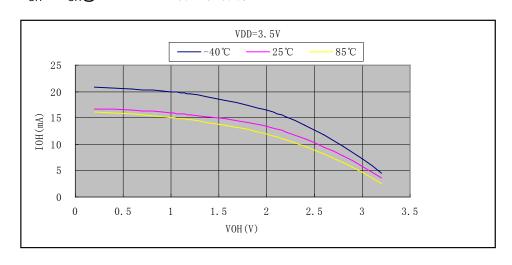

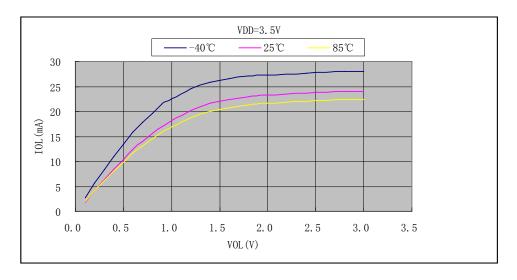

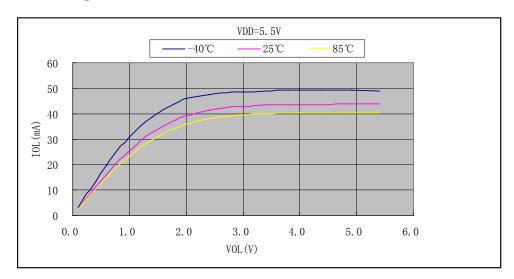

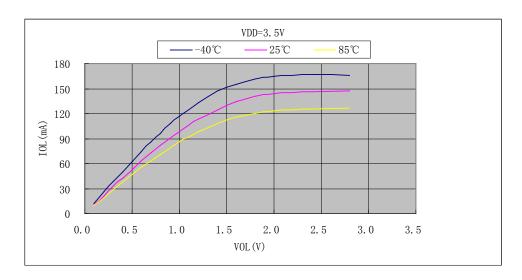

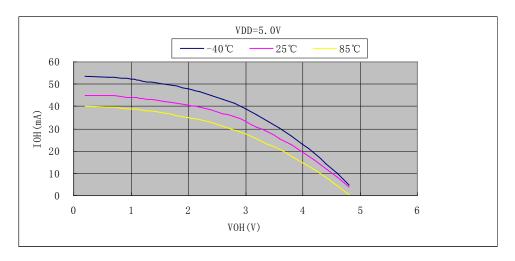

|   | 20. 2. 3  | 芯片 IO 端口输出特性(普通驱动,PA6~PA13 端口除外)  |     |

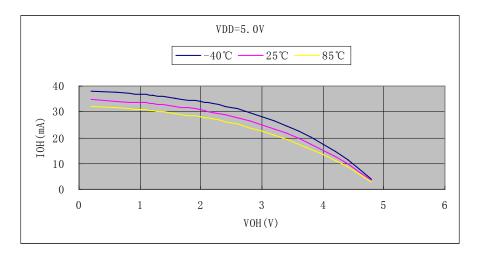

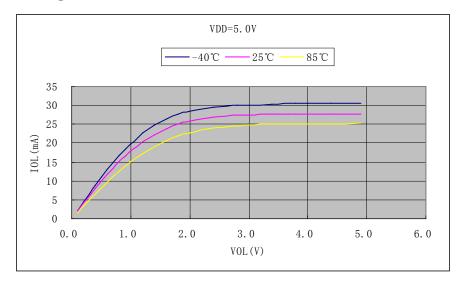

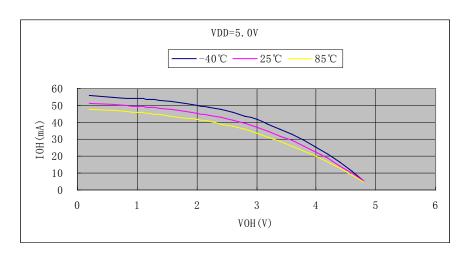

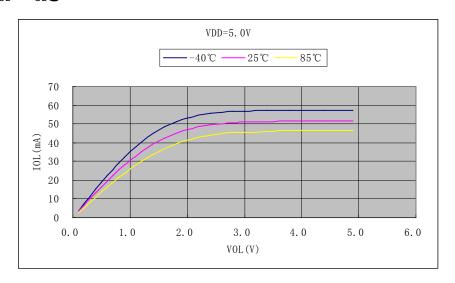

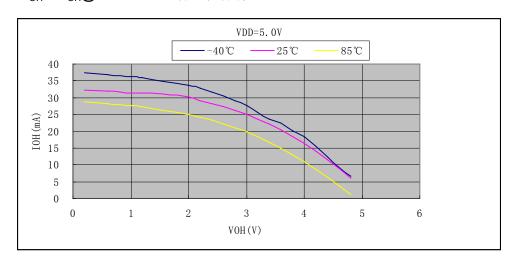

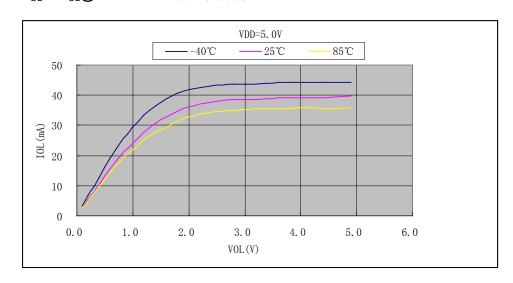

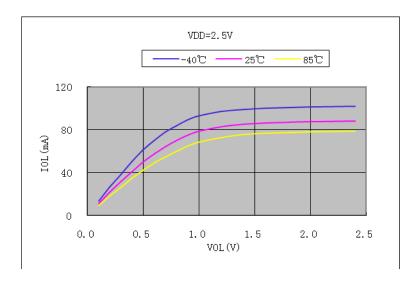

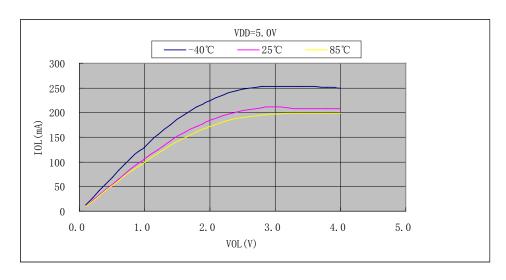

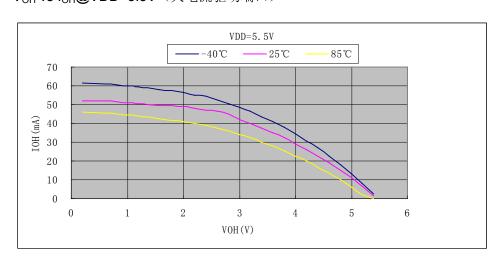

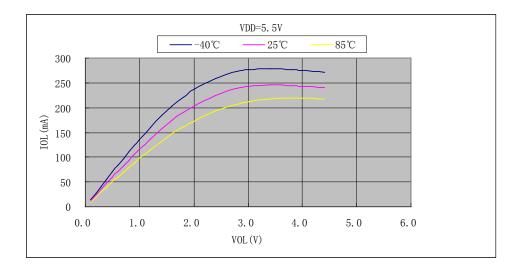

|   | 20. 2. 4  | 芯片 IO 端口输出特性(大电流驱动,PA6~PA13 端口除外) |     |

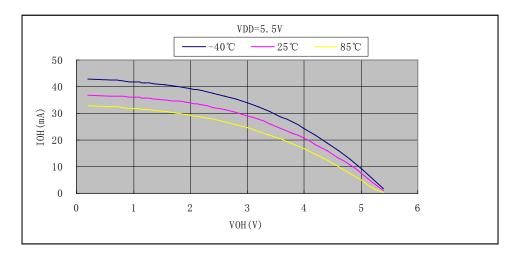

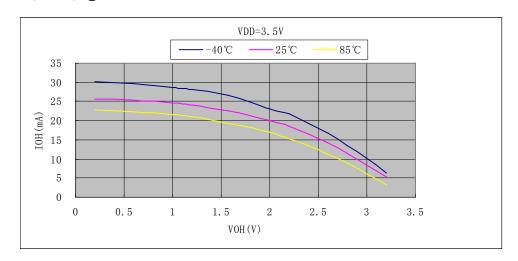

|   | 20. 2. 5  | 芯片 IO 端口输出特性(普通驱动,PA6~PA13 端口)    |     |

|   | 20. 2. 6  | 芯片 IO 端口输出特性(大电流驱动,PA6~PA13 端口)   |     |

|   | 20. 3     | RF 收发器电气特性                        |     |

|   | 20. 3. 1  | 功耗参数                              |     |

|   | 20. 3. 2  | 接收机(RX)参数                         |     |

|   | 20. 3. 3  | 发射机(TX)参数                         |     |

|   | 20. 3. 4  | 频率合成器参数                           |     |

|   | 20. 3. 5  | 振荡器参数                             |     |

| 第 | 21 章      | 编程调试接口                            |     |

|   | 21. 1     | 概述                                |     |

|   | 21. 2     | ISP 编程接口                          |     |

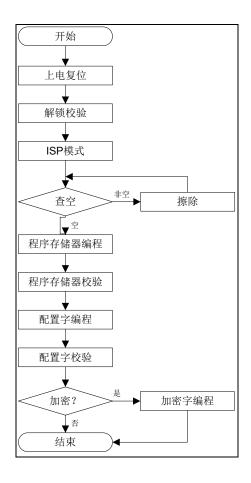

|   | 21. 2. 1  | 通信协议                              | 350 |

| 21. 2. 2 | 操作流程     | 351 |

|----------|----------|-----|

| 21. 3    | SWD 调试接口 | 351 |

| 21. 3. 1 | 概述       | 351 |

| 21 3 2   | SWD 特性   | 352 |

## 图目录

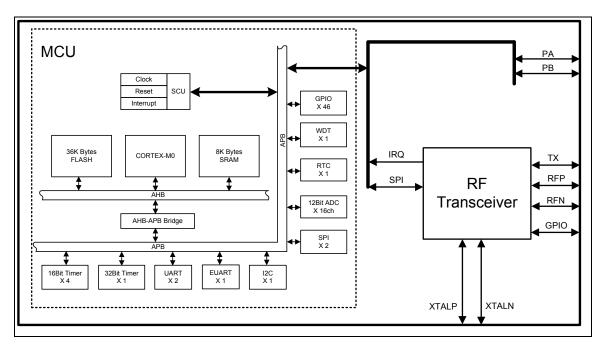

| 图 | 1-1  | 系统内部结构框图                  | .21  |

|---|------|---------------------------|------|

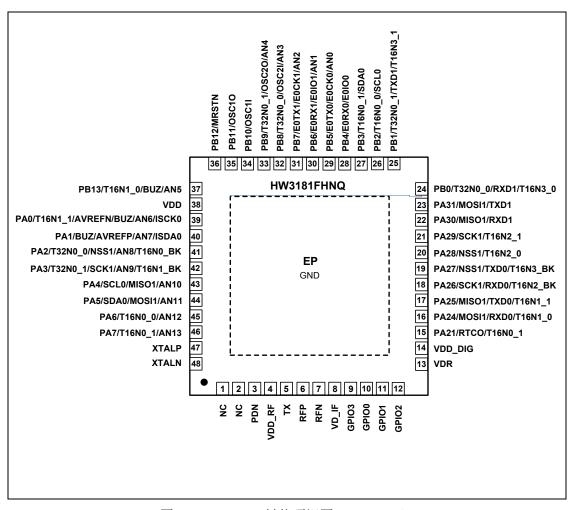

| 图 | 1-2  | QFN48 封装顶视图(TopView)      | . 22 |

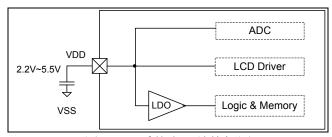

| 图 | 2-1  | 系统电源结构框图                  | . 28 |

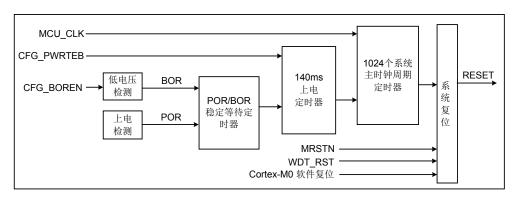

| 图 | 2-2  | 系统复位电路结构框图                | . 28 |

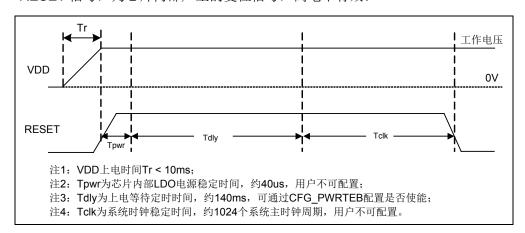

| 图 | 2-3  | 上电复位时序示意图                 | .29  |

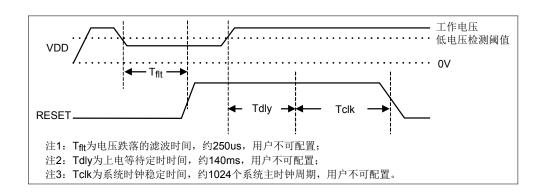

| 图 | 2-4  | 掉电复位时序示意图                 | . 29 |

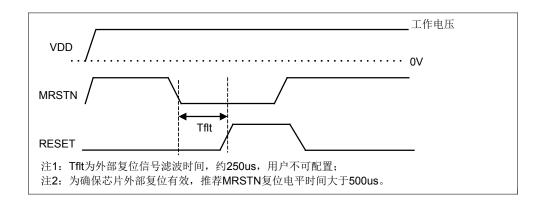

| 图 | 2-5  | 外部复位时序示意图                 | 29   |

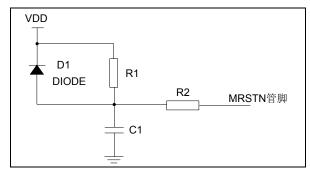

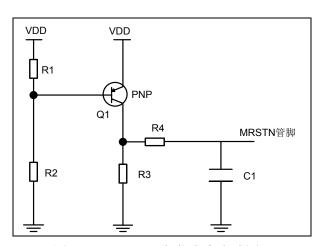

| 图 | 2-6  | MRSTN 复位参考电路图 1           | .30  |

| 图 | 2-7  | MRSTN 复位参考电路图 2           | .30  |

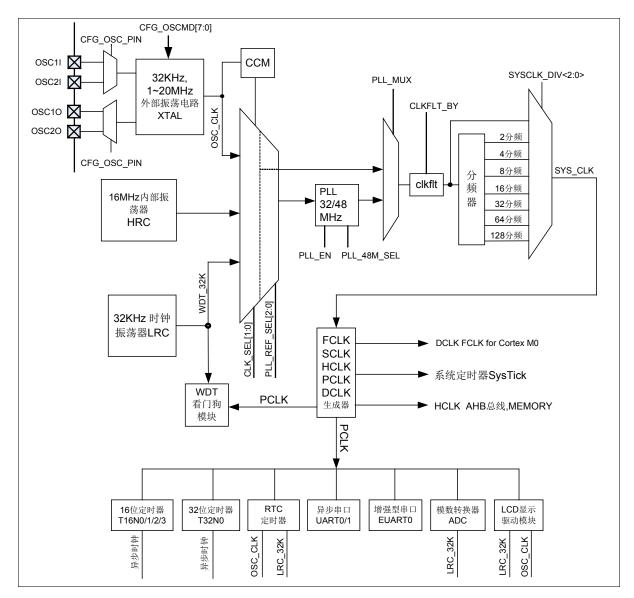

| 图 | 2-8  | 系统时钟电路结构框图                | 38   |

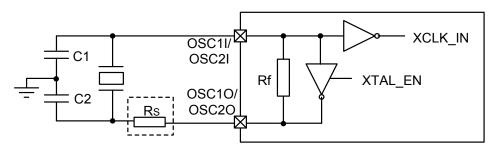

| 图 | 2-9  | XTAL 振荡器电路结构示意图           | 39   |

| 图 | 2-10 | 系统定时器框图                   | 69   |

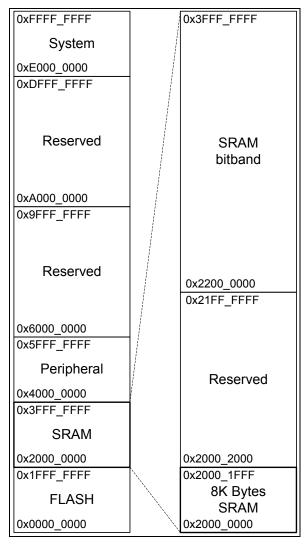

| 图 | 3-1  | 内部存储系统分配示意图               | 75   |

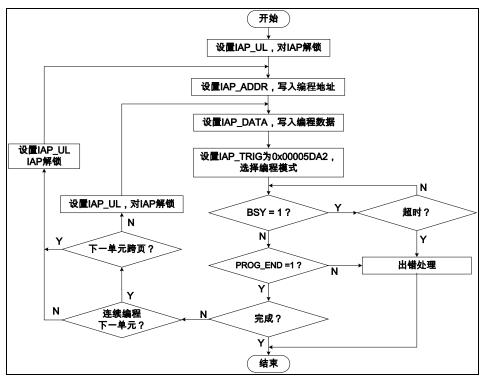

| 图 | 3-2  | IAP 操作请求流程图               | 79   |

| 图 | 3-3  | IAP 全擦除操作流程图              | 80   |

| 图 | 3-4  | IAP 页擦除操作流程图              | 80   |

| 图 | 3-5  | IAP 编程操作流程图               | 81   |

| 图 | 3-6  | SRAM 映射图                  | 86   |

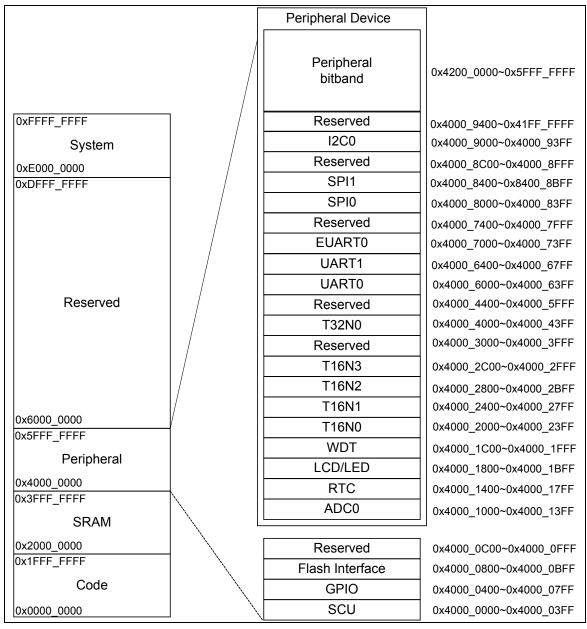

| 图 | 3-7  | 外设存储器分配示意图                | 87   |

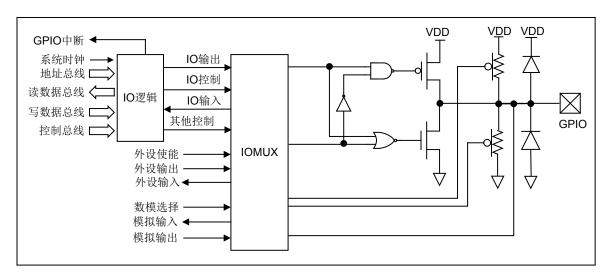

| 图 | 4-1  | IO 端口电路结构图                | 97   |

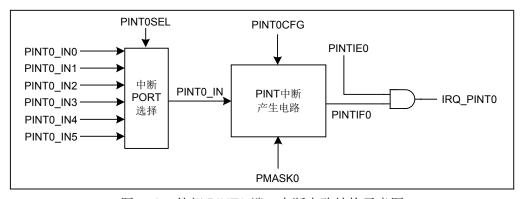

| 图 | 4-2  | 外部 PINT0 端口中断电路结构示意图      | 97   |

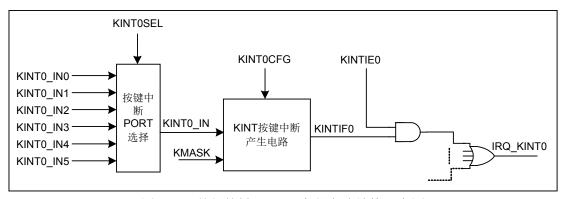

| 图 | 4-3  | 外部按键 KINTO 中断电路结构示意图      | 98   |

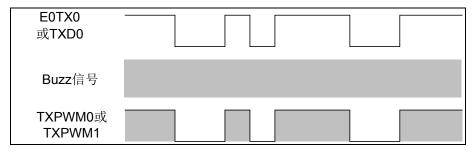

| 图 | 4-4  | Buzz 高电平调制输出波形图           | 99   |

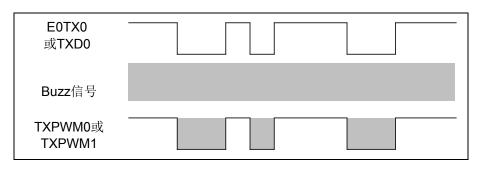

| 图 | 4-5  | Buzz 低电平调制输出波形图           | 100  |

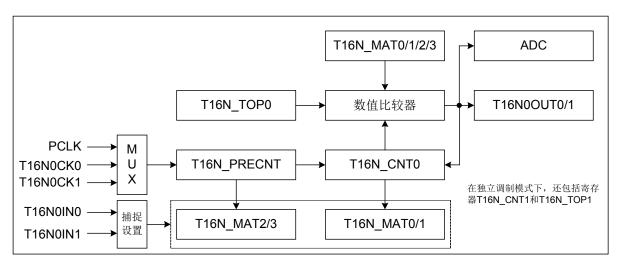

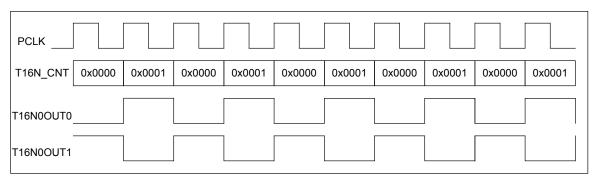

| 图 | 5-1  | T16N0 电路结构框图              | 126  |

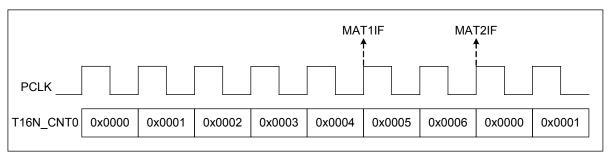

| 图 | 5-2  | T16N0 计数匹配功能示意图           | 127  |

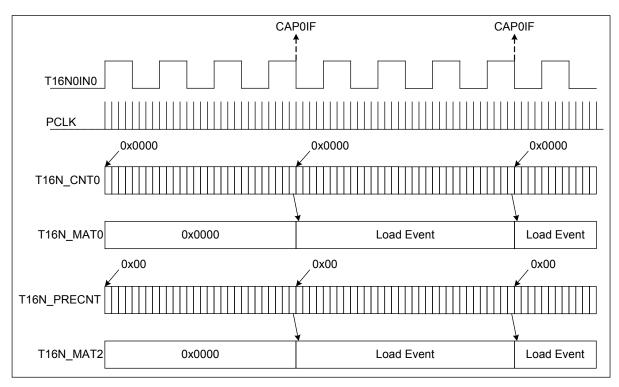

| 图 | 5-3  | T16N0 捕捉功能示意图             | 129  |

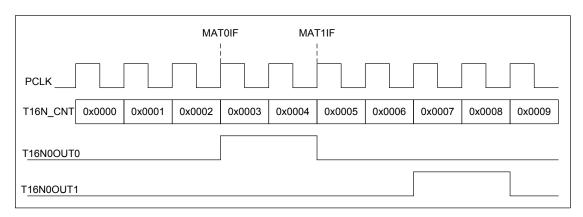

| 图 | 5-4  | T16N0 独立 PWM 输出功能示意图      | 131  |

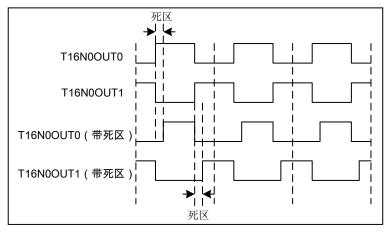

| 图 | 5-5  | T16N0 互补 PWM 输出功能示意图      | 132  |

| 图 | 5-6  | 带死区的 T16N0 互补 PWM 输出功能示意图 | 132  |

| 图 | 5-11 | UART 电路结构图                | 157  |

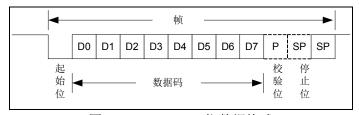

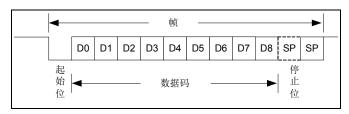

| 图 | 5-12 | UART 7 位数据格式              | 158  |

| 图 | 5-13 | UART 8 位数据格式              | 158  |

| 图 | 5-14 | UART 9 位数据格式              | 158  |

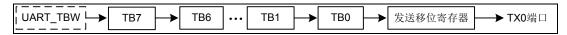

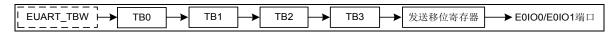

| 图 | 5-15 | UART0 发送数据流示意图            | 159  |

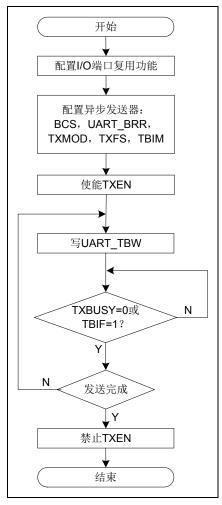

| 图 | 5-16 | UART0 发送数据操作流程图示例         | 160  |

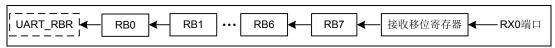

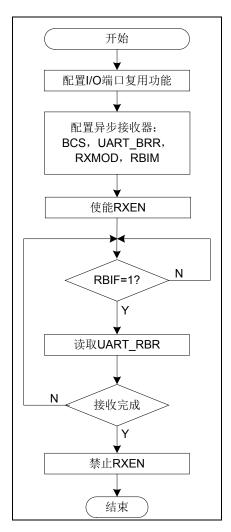

| 图 | 5-17 | UART0 接收数据流示意图            | 161  |

| 图 | 5-18 | UART0 接收数据操作流程图示例         | 162  |

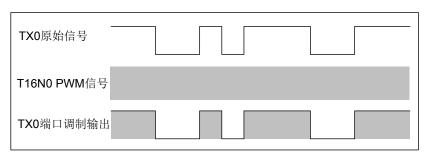

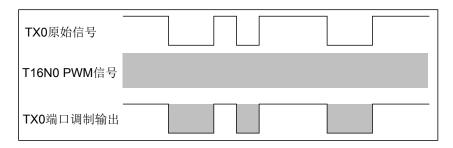

| 图 | 5-19 | TX0 高电平调制输出波形图            |      |

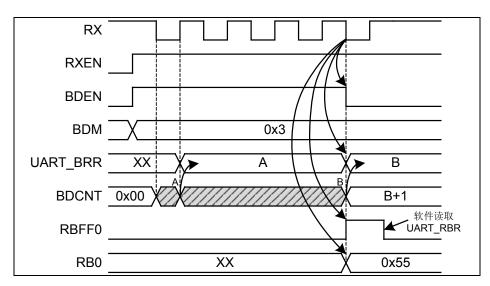

| 图 | 5-21 | 自动波特率检测时序示意图              | 164  |

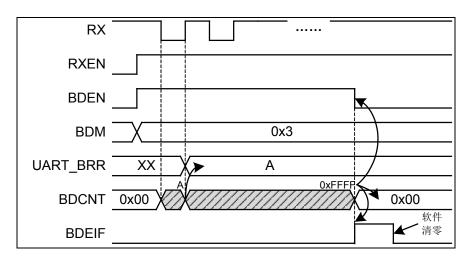

| 图 | 5-22 | 自动波特率检测错误时序示意图            |      |

|   | 5-23 |                           |      |

|   |      | EUARTO 电路结构框图             |      |

|   |      |                           |      |

V1.5

11/352

| 日 5-26 7816 通讯検式技吹数据流示意图 184 图 5-27 SPIO 电路结构框图 198 日 5-28 SPIO 时叶上升沿发送、下降沿接收波形示意图 199 图 5-29 SPIO 时叶下阵沿发送、上升沿接收波形示意图 199 图 5-31 SPIO 时叶下阵沿发送、上升沿接收波形示意图 200 图 5-32 SPIO 技数据流示意图 200 图 5-32 SPIO 技数据流示意图 201 图 5-34 SPI 延迟接收功能波形示意图 201 图 5-34 SPI 延迟接收功能波形示意图 203 医 5-35 I2C 电路结构框图 211 图 5-36 I2C 是战品讯协议示意图 211 图 5-37 I2C 主控器写入从功器数据示意图 211 图 5-38 I2C 主控器导及从功器数据示意图 211 图 5-39 开漏输出端口示意图 212 图 5-39 开漏输出端口示意图 213 图 5-41 I2C 发送数据流示意图 215 图 5-42 I2C 建收数据流示意图 215 图 5-43 I2C 运放数据流示意图 216 图 5-44 I2C 应送数据流示意图 216 图 5-41 I2C 发送数据流示意图 217 图 5-43 I2C 起始位波形图 216 图 5-44 I2C 自动身呼波形图 216 图 5-44 I2C 自动身呼波形图 216 图 5-44 I2C 自动身呼波形图 216 图 5-45 I2C 停止位波形图 216 图 5-47 I2C 数据帧使输问隔功能波形示意图 217 图 5-47 I2C 数据帧使的问隔功能波形示意图 217 图 5-47 I2C 数据帧使的问隔功能波形示意图 217 图 5-47 I2C 数据帧中介示意图 217 图 5-48 I2C 中域 下表面图 227 图 5-48 I2C 中域 下表面图 227 图 5-49 ADC 内部结构图 227 图 5-51 ADC 数据转换即广示意图 218 图 6-2 芯片上电进入发送模式示意图 255 图 7-1 增强型帕结构示意图 255 图 7-1 增强型帕结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 10-1 FIFO 控制示意图 266 图 10-2 两种帧结构技像大学音操作示意图 267 图 10-3 直接 FIFO 帧结构对表像 256 图 10-5 IRQ 中断结由示意图 266 图 10-1 IPC 控制可意图 266 图 10-1 PTX 自动重传情况 1中断示意图 266 图 10-1 PTX 自动重传情况:中断示意图 266 图 10-1 PTX 自动重校情况:中断示意图 266 图 10-1 PTX 自动重校技术形成 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 图 | 5-25  | 7816 通讯模式发送数据流示意图                          | 184 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|--------------------------------------------|-----|

| 图 5-28 SPIO 时钟上升沿发送、下降沿接收波形示意图 199 图 5-29 SPIO 时钟下降沿发送、上升沿接收波形示意图 199 图 5-29 SPIO 时钟下降沿发送、上升沿接收波形示意图 200 图 5-31 SPIO 时钟下降沿接收,上升沿发送波形示意图 200 图 5-33 SPIO 接收数据流示意图 201 图 5-34 SPI 延送城牧功能被形示意图 201 图 5-34 SPI 延送城牧功能被形示意图 203 图 5-35 I2C 电路站构框图 211 图 5-36 I2C 总线通讯协议示意图 211 图 5-37 I2C 生空器写入从动器数据示意图 211 图 5-39 开漏输出端口示意图 212 图 5-39 开漏输出端口示意图 213 图 5-39 开漏输出端口示意图 213 图 5-39 开漏输出端口示意图 213 图 5-41 I2C 发送数据流示意图 214 图 5-42 I2C 接收数据流示意图 215 图 5-43 I2C 电始位波形图 216 图 5-44 I2C 自动当呼波形图 216 图 5-45 I2C 停止位波形图 216 图 5-47 I2C 数据帧传输问隔功能波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 218 图 5-49 ADC 内部结构图 227 图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1,硬件控制采样) 229 图 6-1 RF 收发器状态控制示意图 255 I2C 序 Le 进入发达模式示意图 255 I2C 序 Le 进入发达模式示意图 255 I2C 序 Le 进入接收模式示意图 256 I2C 芯片上电进入接收模式示意图 256 I2C 两种帧结构模式下 FIFO 结构 256 I2C 两种帧结构模式下 FIFO 结构 256 I2C 两种结构模式下 FIFO 结构 256 I2C 两种结构模式下 FIFO 结构 256 I2C 两种统结构模式下 FIFO 结构 256 I2C 两种统结构或 256 I2C 两种统结构模式下 FIFO 结构 256 I2C 两种统结构模式下 FIFO 结构 256 I2C 两种统由示意图 256 I2C 中断示意图 256 I2C 中断示意图 256 I2C 中断 256 I2C P2C I2C P2C I2C P2C P2C P2C P2C P2C P2C P2C P2C P2C P            | 图 | 5-26  | 7816 通讯模式接收数据流示意图                          | 184 |

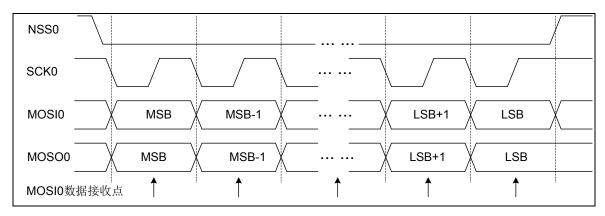

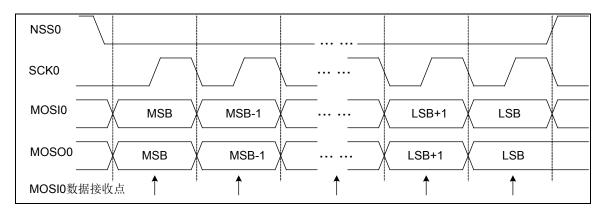

| 图 5-29 SP10 时钟下降沿发达,上升沿接收波形示意图 200 图 5-31 SP10 时钟下降沿接收,上升沿发送波形示意图 200 图 5-32 SP1 发达数据流示意图 200 图 5-32 SP1 发达数据流示意图 201 图 5-34 SP1 延迟接收功能波形示意图 203 SP10 接收数据流示意图 201 图 5-34 SP1 延迟接收功能波形示意图 203 图 5-35 I2C 电路结构框图 210 图 5-36 I2C 总线通讯协议示意图 211 图 5-36 I2C 总线通讯协议示意图 211 图 5-36 I2C 总线通讯协议示意图 211 图 5-37 I2C 主控器写入从功器数据示意图 211 图 5-39 开漏输出端口示意图 212 图 5-39 开漏输出端口示意图 213 图 5-41 I2C 发送数据流示意图 214 图 5-42 I2C 接收数据流示意图 215 图 5-42 I2C 接收数据流示意图 216 图 5-45 I2C 使业位波形图 216 图 5-45 I2C 使业位波形图 216 图 5-45 I2C 应始位波形图 216 图 5-46 I2C 回动手呼波形图 216 图 5-47 I2C 数据帧传输间隔功能波形示意图 217 图 5-47 I2C 数据帧传输间隔功能波形示意图 227 图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1,硬件控制采样) 229 图 6-1 RF 收发器状态控制示意图 253 图 6-2 芯片上电进入发送模式示意图 256 图 7-1 增强型帧结构示意图 257 图 6-3 芯片上电进入发送模式示意图 258 图 7-1 增强型帧结构示意图 258 图 7-1 增强型帧结构示意图 259 图 6-3 芯片上电进入设送模式示意图 258 图 7-1 增强型帧结构表示序图 258 图 7-2 直接 FIFO 帧结构交送单空操作示意图 258 图 10-1 FIFO 控制示意图 268 图 10-5 IRQ 中断端相示意图 268 图 10-5 IRQ 中断端相示意图 269 I10-1 PRX 自动重传情况 2 中断示意图 268 I10-1 PRX 自动重传情况 2 中断示意图 268 I10-1 PRX 自动重传情况 3 中断示意图 268 I10-1 PRX 自动重传情况 3 中断示意图 269 I10-10 PTX 自动重传情况 3 中断示意图 266 I10-11 PRX 自动重传情况 3 中断示意图 266 I10-11 PRX 自动重传情况 3 中断示意图 266 I10-11 PRX 自动重传情况 3 中断示意图 266 I10-12 PTX 自动重传情况 3 中断示意图 266 I10-13 直接 FIFO 帧结构中断示意图 267 I10-12 ACK 使能情况下 NOACK 功能中断示意图 268 I10-13 直接 FIFO 帧结构中断示意图 269 I10-11 PRX 自动重传形式 3 中断示意图 269 I10-11 PRX 自动重传情况 3 中断示意图 269 I10-11 PRX 自动重传形式 3 中断示意图 269 I10-11 PRX 自动重传形式 3 中断示意图 269 I10-11 PRX 自动重传形式 3 中断示意图 269 I10-12 ACK 使能情况 NOACK 功能中影形表 269 I10-11 PRX 自动重传形式 3 中标示意图 269 I10-12 ACK 使能情况 5 中标示意图 269 I10-13 直接 FIFO 帧结构中断示意图 269 I10-14 ACK 使能情况 5 中标示意图 269 I10-14 ACK 使能力量 5 中标示意图 269 I10-14 ACK 使能力量 5 中标示意图 269 I10-14 ACK 使能  | 图 | 5-27  | SPI0 电路结构框图                                | 198 |

| 图 5-31 SP10 时钟下降沿接收,上升治发送波形示意图 200 图 5-32 SP1 发送数据流示意图 200 图 5-32 SP1 发送数据流示意图 201 图 5-33 SP10 接收数据流示意图 201 图 5-34 SP1 延迟接收功能波形示意图 203 图 5-35 I2C 电路结构框图 210 图 5-36 I2C 总线通讯协议示意图 211 图 5-37 I2C 主控器写入从功器数据示意图 211 图 5-37 I2C 主控器词入从功器数据示意图 212 图 5-38 I2C 主控器读取从功器数据示意图 212 图 5-38 I2C 生控器读取从功器数据示意图 212 图 5-34 I2C 支送数据流示意图 213 图 5-41 I2C 发送数据流示意图 215 图 5-42 I2C 接收数据流示意图 216 图 5-42 I2C 自动寻呼波形图 216 图 5-43 I2C 起始位波形图 216 图 5-44 I2C 自动寻呼波形图 216 图 5-45 I2C 停止位波形图 216 图 5-46 I2C 应答延迟功能波形示意图 217 图 5-47 I2C 数据帧传输间隔户能波形示意图 227 图 5-48 I2C 时钟线下拉等待波形示意图 218 5-48 I2C 时钟线下拉等待波形示意图 227 图 5-48 I2C 时进入发达模式示意图 227 图 5-48 I2C 时进入发达模式示意图 255 图 6-3 芯片上电进入发达模式示意图 255 图 6-1 RF 收发器状态控制示意图 255 图 6-1 RF 收发器状态控制示意图 255 图 6-2 芯片上电进入接收模式示意图 255 图 6-1 中于下直、接下FPO 帧结构示意图 256 图 10-1 FPO 控制示意图 256 图 10-1 FIFO 校结构技论学学操作示意图 256 图 10-1 FIFO 校结构技论学学操作示意图 268 图 10-1 IFFO 校结构技论学学操作示意图 268 图 10-1 IFFO 校结构技论学学操作示意图 268 图 10-1 IFFO 校结构技论学节操作示意图 268 图 10-1 IFFO 校结构技论学学操作示意图 268 图 10-1 PFX 自动重传情况 1 中断示意图 266 图 10-10 PTX 自动重传情况 2 中断示意图 266 图 10-10 PTX 自动重传情况 3 中断示意图 266 图 10-10 PTX 自动重传情况 3 中断示意图 266 图 10-11 PTX 自动重传情况 3 中断示意图(重传起时,重传次数为 2) 266 图 10-10 PTX 自动重传情况 3 中断示意图(重传起时,重传次数为 2) 266 图 10-11 PTX 自动重传情况 3 中断示意图(重传起时,重传次数为 2) 266 图 10-11 PTX 自动重传情况 3 中断示意图(重传起时,重传次数为 2) 266 图 10-11 PTX 自动重传形式 3 中断示意图(重传起时,重传次数为 2) 266 图 10-11 PTX 自动重传形式 3 中断示意图(267 图 10-12 ACK 使能行况 5 PM 2 PM                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 图 | 5-28  | SPI0 时钟上升沿发送,下降沿接收波形示意图                    | 199 |

| 图 5-32 SPI 发达数据流示意图 201 图 5-33 SPIO 接收数据流示意图 201 图 5-34 SPI 延迟核收功能液形示意图 203 图 5-34 SPI 延迟核收功能液形示意图 203 图 5-36 I2C 电路结构框图 210 图 5-36 I2C 电路结构框图 210 图 5-37 I2C 主控器诗入从动器数据示意图 211 图 5-37 I2C 主控器诗入从动器数据示意图 212 图 5-39 H漏输出端口示意图 213 图 5-39 H漏输出端口示意图 213 图 5-49 I2C 技数数据流示意图 214 图 5-41 I2C 发达数据流示意图 215 图 5-43 I2C 电始价波形图 216 图 5-44 I2C 自动寻呼波形图 216 图 5-44 I2C 自动寻呼波形图 216 图 5-45 I2C 停止位波形图 216 图 5-46 I2C 应答延迟功能波形示意图 217 图 5-47 I2C 发掘帧传输间隔页能波形示意图 217 图 5-48 I2C 时钟线下拉等符波形示意图 227 图 5-49 ADC 内部结构图 227 图 5-49 ADC 内部结构图 227 图 5-49 ADC 内部结构图 250 图 7-1 增强型帧结构示意图 255 图 6-2 芯片上电进入技线模式示意图 255 图 6-3 芯片上电进入技线模式示意图 256 图 7-1 增强型帧结构示意图 256 图 7-1 增强型帧结构示意图 257 图 5-1 4 PIPE 通讯示意图 256 图 7-1 增强型帧结构表意图 257 图 5-1 10-1 增强型帧结构表意图 256 图 7-1 增强型帧结构表意图 256 图 7-1 增强型帧结构表意图 256 图 7-1 增强型帧结构表意图 256 图 7-1 均强型帧结构表音图 256 图 10-2 两种帧结构模式下FIFO 结构 256 图 10-1 TPC 对的域体的模式中断示意图 260 图 10-2 两种帧结构技改生消费作示意图 260 图 10-1 IPC 对的域体的设定半消费作示意图 262 图 10-1 1PTX 自动重传情况 1 中断示意图 266 图 10-9 PTX 自动重传情况 1 中断示意图 266 图 10-9 PTX 自动重传情况 1 中断示意图 266 图 10-1 PTX 自动重传情况 1 中断示意图 266 图 10-1 PTX 自动重传情况 1 中断示意图 266 图 10-10 PTX 自动重传情况 1 中断示意图 266 图 10-11 PRX 自动重使中断示意图 266 图 10-11 PRX 自动重使中断示意图 266                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 图 | 5-29  | SPI0 时钟下降沿发送,上升沿接收波形示意图                    | 199 |

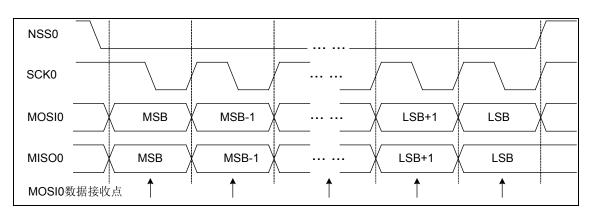

| 图 5-33 SPIO 接收数据流示意图 201 图 5-34 SPI 建迟接收功能波形示意图 203 图 5-35 I2C 电路结构框图 210 图 5-36 I2C 总线通讯协议示意图 211 图 5-37 I2C 主控需导入从动器数据示意图 211 图 5-37 I2C 主控需诗取从动器数据示意图 212 图 5-38 I2C 主控器诗取从动器数据示意图 212 图 5-39 开漏输出端口示意图 213 图 5-41 I2C 发送数据流示意图 214 图 5-42 I2C 接收数据流示意图 214 图 5-44 I2C 自动寻呼波形图 216 图 5-45 I2C 使止位波形图 217 I2C 数据帧传输问隔功能波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 217 图 5-48 I2C 时钟线下拉等待波形示意图 218 图 5-49 ADC 内部结构图 227 图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样) 229 图 6-1 RF 收发器状态控制示意图 256 图 6-2 芯片上电进入接收模式示意图 256 图 7-1 增强型帧结构示意图 256 图 10-1 FIFO 控制示意图 258 图 10-1 FIFO 控制示意图 268 图 10-1 FIFO 拉结构接收半满操作示意图 268 图 10-1 FIFO 拉结构接收半满操作示意图 268 图 10-1 FIFO 如重传情况 1 中断示意图 269 图 10-10 PTX 自动重传情况 3 中断示意图 269 图 10-11 PRX 自动重使情况 3 中断示意图 269 图 10-11 PRX 自动重使描记 4 PFX 自动重使制示意图 269 图 10-11 PRX 自动重使式 4 PFX 自动重使 4 PFX 自动 4 PFX | 图 | 5-31  | SPI0 时钟下降沿接收,上升沿发送波形示意图                    | 200 |

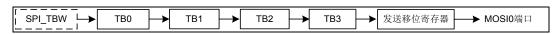

| 图 5-34 SPI 延迟接收功能波形示意图 203 图 5-35 12C 电路结构框图 210 图 5-36 12C 总线通讯协议示意图 211 图 5-37 12C 主控器写入从动器数据示意图 211 图 5-37 12C 主控器写入从动器数据示意图 212 图 5-38 12C 主控器写入从动器数据示意图 212 图 5-39 开漏输出端口示意图 213 图 5-41 12C 发送数据流示意图 214 图 5-42 12C 接收数据流示意图 215 图 5-43 12C 起始仪波形图 216 图 5-44 12C 自动寻呼波形图 216 图 5-45 12C 应存证迟功能波形示意图 216 图 5-44 12C 自动寻呼波形图 216 图 5-44 12C 自动寻呼波形图 216 图 5-45 12C 数据帧传输间隔功能波形示意图 217 图 5-47 12C 数据帧传输间隔功能波形示意图 218 图 5-48 12C 时钟线下拉等符波形示意图 218 图 5-49 ADC 内部结构图 227 图 6-1 RF 收发器状态控制示意图 229 图 6-1 RF 收发器状态控制示意图 256 图 7-1 增强型帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-2 直接 FIFO 帧结构示意图 256 图 7-1 增强型帧结构示意图 256 图 7-2 直接 FIFO 帧结构表文章 图 256 图 10-1 FIFO 控制示意图 258 图 10-1 FIFO 射结构接收半满操作示意图 258 图 10-1 FIFO 射结构接收半满操作示意图 258 图 10-1 互接 FIFO 帧结构接收半满操作示意图 258 图 10-1 PTX 自动重传情况 1 中断示意图 258 图 10-1 ACK 使能话常证中断示意图 258 图 10-1 PTX 自动重传情况 2 中断示意图 258 图 10-1 PTX 自动重传情况 3 中断示意图 256 图 10-10 PTX 自动重传情况 3 中断示意图 256 图 10-10 PTX 自动重传情况 3 中断示意图 256 图 10-11 PTX 自动重传情况 3 中断示意图 256 图 10-12 ACK 使能情况下 NOACK 功能中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-14 ACK 使能情况下 NOACK 功能中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-14 ACK 使能情况下 NOACK 功能中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-14 ACK 使能情况下 NOACK 功能中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-14 ACK 使能情况下 NOACK 功能中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中断示意图 258 图 10-13 直接 FIFO 帧结构中标示意图 258 图 10-13 直接 FIFO 帧结构 20 中标示记述 20 中标记述 20 | 图 | 5-32  | SPI 发送数据流示意图                               | 200 |

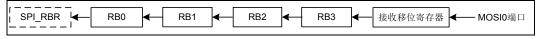

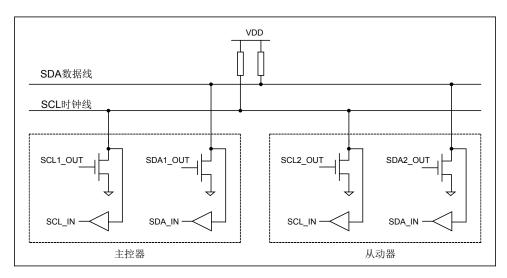

| 图 5-35   I2C 电路结构框图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 图 | 5-33  | SPI0 接收数据流示意图                              | 201 |

| 図 5-36   2C 总线通讯协议示意图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 图 | 5-34  | SPI 延迟接收功能波形示意图                            | 203 |

| 图 5-37       12C 主控器写入从动器数据示意图       212         图 5-38       12C 主控器读取从动器数据示意图       213         图 5-41       12C 发送数据流示意图       214         图 5-42       12C 接收数据流示意图       215         图 5-43       12C 应好效数据流示意图       216         图 5-44       12C 自动寻呼波形图       216         图 5-44       12C 自动寻呼波形图       216         图 5-45       12C 停止位波形图       216         图 5-46       12C 应答延迟功能波形示意图       217         图 5-47       12C 数据帧传输间隔功能波形示意图       217         图 5-48       12C 时钟线下拉等待波形示意图       218         图 5-49       ADC 内部结构图       227         图 5-51       ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)       229         图 6-1       RF 收发器状态控制示意图       253         图 6-2       芯片上电进入接收模式示意图       255         图 6-3       芯片上电进入发送模式示意图       255         图 7-1       增强型帧结构示意图       255         图 7-2       直接 FIFO 帧结构示意图       256         图 7-2       直接 FIFO 帧结构示意图       260         图 10-2       两种帧结构技术下 FIFO 结构       261         图 10-2       两种帧结构体校长平清操作示意图       262         图 10-3       直接 FIFO 帧结构技术下 序列       262         图 10-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 图 | 5-35  | I2C 电路结构框图                                 | 210 |

| 图 5-38       12C 主控器读取从动器数据示意图       212         图 5-41       12C 发送数据流示意图       214         图 5-42       12C 接收数据流示意图       215         图 5-43       12C 起始位波形图       216         图 5-44       12C 自动寻呼波形图       216         图 5-44       12C 自动寻呼波形图       216         图 5-44       12C 停止位波形图       216         图 5-44       12C 应答延迟功能波形示意图       217         图 5-45       12C 应答延迟功能波形示意图       217         图 5-46       12C 时钟线下拉等待波形示意图       217         图 5-47       12C 数据帧传输间隔功能波形示意图       218         图 5-48       12C 时钟线下拉等待波形示意图       218         图 5-49       ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)       229         图 5-11       RP 收费米水态控制示意图       255         图 6-1       RF 收支楼水态控制示意图       255         图 6-2       芯片上电进入发送模式示意图       255         图 6-3       芯片上电进入发送模式示意图       255         图 7-1       增强型帧结构示意图       255         图 7-2       直接 FIFO 帧结构示意图       266         图 10-1       FIFO 控制小壳宽图       268         图 10-2       两种帧结构技术下序区       260         图 10-3       直接 FIFO 帧结构成水下流域、标准       262         图 10-6       AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 图 | 5-36  | I2C 总线通讯协议示意图                              | 211 |

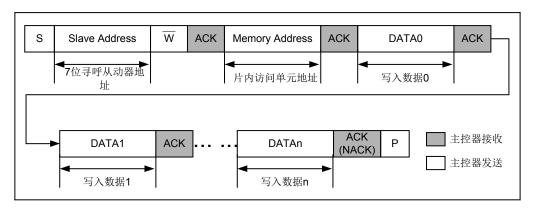

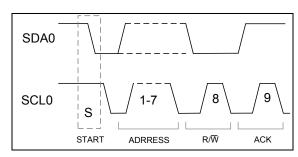

| 图 5-39 开編输出端口示意图 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 图 | 5-37  | I2C 主控器写入从动器数据示意图                          | 212 |

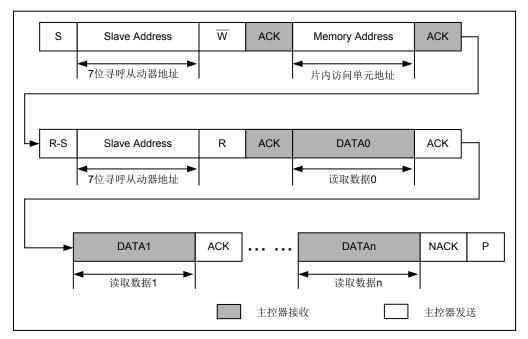

| 图 5-41       12C 发送数据流示意图       214         图 5-42       12C 接收数据流示意图       215         图 5-43       12C 起始位波形图       216         图 5-44       12C 自动寻呼波形图       216         图 5-45       12C 应答延迟功能波形示意图       217         图 5-46       12C 应答延迟功能波形示意图       217         图 5-47       12C 数据帧传输间隔功能波形示意图       217         图 5-48       12C 时钟线下拉等待波形示意图       218         图 5-49       ADC 內部结构图       227         图 5-51       ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)       229         图 6-1       RF 收发器状态控制示意图       253         图 6-2       芯片上电进入发送模式示意图       255         图 7-1       增强型域结构示意图       255         图 7-2       直接 FIFO 帧结构示意图       256         图 7-2       直接 FIFO 帧结构示意图       258         图 10-1       FIFO 控制示意图       260         图 10-2       两种帧结构模式下 FIFO 结构       261         图 10-3       直接 FIFO 帧结构发送半空操作示意图       262         图 10-4       直接 FIFO 帧结构技收率消操作示意图       262         图 10-5       IRQ 中断输出示意图       265         图 10-6       ACK 使能计况中断示意图       265         图 10-9       PTX 自动重传情况 1 中断示意图       265         图 10-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 图 | 5-38  | I2C 主控器读取从动器数据示意图                          | 212 |

| 图 5-42 I2C 接收数据流示意图       215         图 5-43 I2C 起始位波形图       216         图 5-44 I2C 自动寻呼波形图       216         图 5-45 I2C 停止位波形图       216         图 5-46 I2C 应答延迟功能波形示意图       217         图 5-47 I2C 数据帧传输间隔功能波形示意图       217         图 5-48 I2C 时钟线下拉等待波形示意图       218         图 5-49 ADC 内部结构图       227         图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)       229         图 6-1 RF 收发器状态控制示意图       255         图 6-2 芯片上电进入发送模式示意图       255         图 6-3 芯片上电进入接收模式示意图       255         图 7-1 增强型帧结构示意图       256         图 7-2 直接 FIFO 帧结构示意图       257         图 8-1 4 路 PIPE 通讯示意图       260         图 10-1 FIFO 控制示意图       260         图 10-2 两种帧结构模式下 FIFO 结构       261         图 10-3 直接 FIFO 帧结构发送半空操作示意图       262         图 10-4 直接 FIFO 帧结构接收半满操作示意图       262         图 10-5 IRQ 中断输出示意图       265         图 10-6 ACK 使能正常通讯中断示意图       265         图 10-7 ACK 使能正常通讯中断示意图       266         图 10-8 PTX 自动重传情况 2 中断示意图       266         图 10-10 PTX 自动重传情况 3 中断示意图       266         图 10-11 PRX 自动重传情况 3 中断示意图       266         图 10-12 ACK 使能情况下 NOACK 功能中断示意图       268         图 10-13 直接 FIFO 帧结构中断示意图<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 图 | 5-39  | 开漏输出端口示意图                                  | 213 |

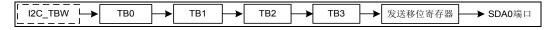

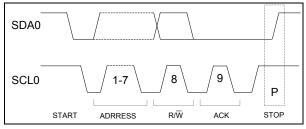

| 图 5-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 图 | 5-41  | I2C 发送数据流示意图                               | 214 |

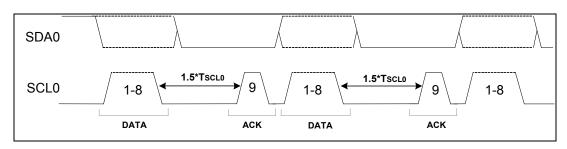

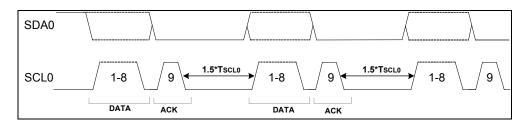

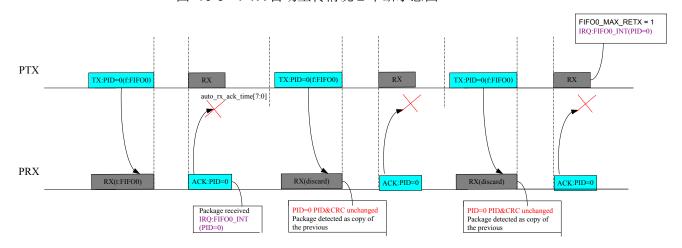

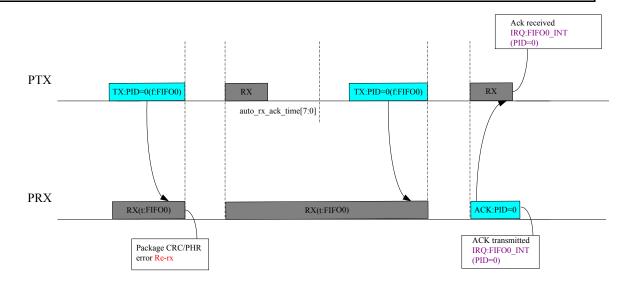

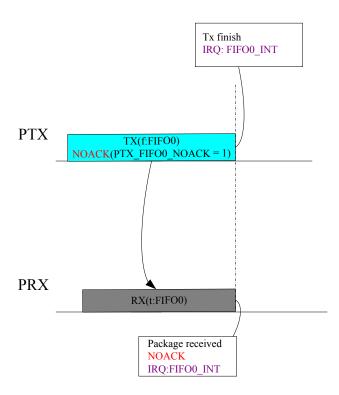

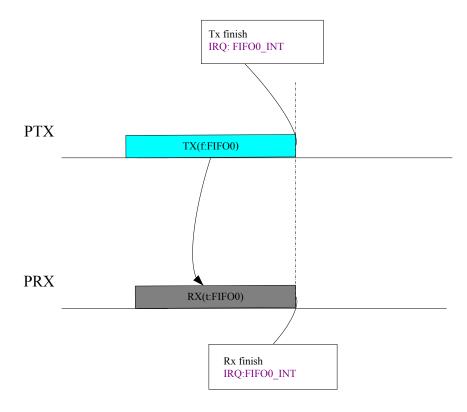

| 图 5-44 I2C 自动寻呼波形图216图 5-45 I2C 停止位波形图216图 5-46 I2C 应答延迟功能波形示意图217图 5-47 I2C 数据帧传输间隔功能波形示意图217图 5-48 I2C 时钟线下拉等待波形示意图218图 5-49 ADC 内部结构图227图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)229图 6-1 RF 收发器状态控制示意图253图 6-2 芯片上电进入发送模式示意图255图 6-3 芯片上电进入接收模式示意图255图 7-1 增强型帧结构示意图256图 7-2 直接 FIFO 帧结构示意图257图 8-1 4 路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图261图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构发送半空操作示意图262图 10-4 直接 FIFO 帧结构发域中消操作示意图262图 10-5 IRQ 中断输出示意图262图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-8 PTX 自动重传情况 1 中断示意图265图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图266图 10-11 PRX 自动重收中断示意图266图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 图 | 5-42  | I2C 接收数据流示意图                               | 215 |

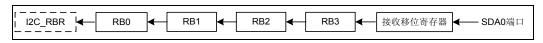

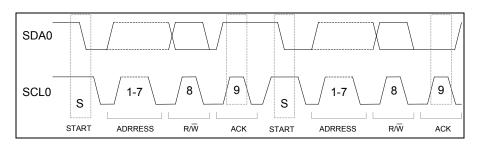

| 图 5-45 I2C 停止位波形图216图 5-46 I2C 应答延迟功能波形示意图217图 5-47 I2C 数据帧传输间隔功能波形示意图217图 5-48 I2C 时钟线下拉等待波形示意图218图 5-49 ADC 内部结构图227图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)229图 6-1 RF 收发器状态控制示意图253图 6-2 芯片上电进入发送模式示意图255图 6-3 芯片上电进入接收模式示意图255图 7-1 增强型帧结构示意图256图 7-2 直接 FIFO 帧结构示意图257图 8-1 4 路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图260图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构发送半空操作示意图262图 10-4 直接 FIFO 帧结构接收半满操作示意图262图 10-5 IRQ 中断输出示意图263图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-8 PTX 自动重传情况 1 中断示意图265图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图266图 10-11 PRX 自动重收中断示意图266图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 图 | 5-43  | I2C 起始位波形图                                 | 216 |

| 图 5-46I2C 应答延迟功能波形示意图217图 5-47I2C 数据帧传输间隔功能波形示意图218图 5-48I2C 时钟线下拉等待波形示意图218图 5-49ADC 内部结构图227图 5-51ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)229图 6-1RF 收发器状态控制示意图253图 6-2芯片上电进入发送模式示意图255图 6-3芯片上电进入发送模式示意图255图 7-1增强型帧结构示意图256图 7-2直接 FIFO 帧结构示意图257图 8-14 路 PIPE 通讯示意图258图 10-1FIFO 控制示意图260图 10-2两种帧结构模式下 FIFO 结构261图 10-3直接 FIFO 帧结构发送半空操作示意图262图 10-4直接 FIFO 帧结构接收半满操作示意图262图 10-5IRQ 中断输出示意图263图 10-6ACK 不使能情况中断示意图265图 10-7ACK 使能情况 1 中断示意图265图 10-8PTX 自动重传情况 2 中断示意图266图 10-9PTX 自动重传情况 2 中断示意图266图 10-10PTX 自动重传情况 3 中断示意图266图 10-11PRX 自动重收中断示意图266图 10-12ACK 使能情况下 NOACK 功能中断示意图268图 10-13直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 图 | 5-44  | I2C 自动寻呼波形图                                | 216 |

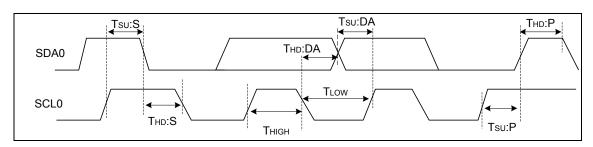

| 图 5-47 I2C 数据帧传输间隔功能波形示意图       217         图 5-48 I2C 时钟线下拉等待波形示意图       218         图 5-49 ADC 内部结构图       227         图 5-51 ADC 数据转换时序示意图(ADC_CON1 寄存器的 SMPS=1,硬件控制采样)       229         图 6-1 RF 收发器状态控制示意图       253         图 6-2 芯片上电进入发送模式示意图       255         图 6-3 芯片上电进入接收模式示意图       255         图 7-1 增强型帧结构示意图       256         图 7-2 直接 FIFO 帧结构示意图       257         图 8-1 4 路 PIPE 通讯示意图       258         图 10-1 FIFO 控制示意图       260         图 10-2 两种帧结构模式下 FIFO 结构       261         图 10-3 直接 FIFO 帧结构发送半空操作示意图       262         图 10-4 直接 FIFO 帧结构接收半满操作示意图       262         图 10-5 IRQ 中断输出示意图       264         图 10-6 ACK 不使能情况中断示意图       265         图 10-7 ACK 使能情况1 中断示意图       265         图 10-8 PTX 自动重传情况2 中断示意图       266         图 10-10 PTX 自动重传情况3 中断示意图       266         图 10-11 PRX 自动重收中断示意图       266         图 10-12 ACK 使能情况下 NOACK 功能中断示意图       268         图 10-13 直接 FIFO 帧结构中断示意图       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 图 | 5-45  | I2C 停止位波形图                                 | 216 |

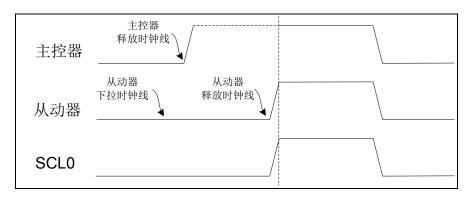

| 图 5-48 I2C 时钟线下拉等待波形示意图       218         图 5-49 ADC 内部结构图       227         图 5-51 ADC 数据转换时序示意图 (ADC_CON1 寄存器的 SMPS=1, 硬件控制采样)       229         图 6-1 RF 收发器状态控制示意图       253         图 6-2 芯片上电进入发送模式示意图       255         图 6-3 芯片上电进入接收模式示意图       255         图 7-2 直接 FIFO 帧结构示意图       256         图 7-2 直接 FIFO 帧结构示意图       257         图 8-1 4路 PIPE 通讯示意图       258         图 10-1 FIFO 控制示意图       260         图 10-2 两种帧结构模式下 FIFO 结构       261         图 10-3 直接 FIFO 帧结构发送半空操作示意图       262         图 10-4 直接 FIFO 帧结构接收半满操作示意图       262         图 10-5 IRQ 中断输出示意图       264         图 10-6 ACK 不使能情况中断示意图       265         图 10-8 PTX 自动重传情况 1 中断示意图       266         图 10-9 PTX 自动重传情况 2 中断示意图       266         图 10-10 PTX 自动重传情况 3 中断示意图       266         图 10-11 PRX 自动重传情况 3 中断示意图       266         图 10-12 ACK 使能情况下 NOACK 功能中断示意图       268         图 10-13 直接 FIFO 帧结构中断示意图       268         图 10-13 直接 FIFO 帧结构中断示意图       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 图 | 5-46  | I2C 应答延迟功能波形示意图                            | 217 |

| 图 5-49 ADC 内部结构图227图 5-51 ADC 数据转换时序示意图(ADC_CON1 寄存器的 SMPS=1,硬件控制采样)229图 6-1 RF 收发器状态控制示意图253图 6-2 芯片上电进入发送模式示意图255图 6-3 芯片上电进入接收模式示意图255图 7-1 增强型帧结构示意图256图 7-2 直接 FIFO 帧结构示意图257图 8-1 4路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图260图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构按送半空操作示意图262图 10-4 直接 FIFO 帧结构接收半满操作示意图262图 10-5 IRQ 中断输出示意图263图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图266图 10-11 PRX 自动重收中断示意图266图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 图 | 5-47  | I2C 数据帧传输间隔功能波形示意图                         | 217 |

| 図 5-51 ADC 数据转换时序示意图(ADC_CON1 寄存器的 SMPS=1,硬件控制采样)2298 6-1 RF 收发器状态控制示意图2538 6-2 芯片上电进入发送模式示意图255图 6-3 芯片上电进入接收模式示意图255图 7-1 增强型帧结构示意图256图 7-2 直接 FIFO 帧结构示意图257图 8-1 4路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图260图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构接收半满操作示意图262图 10-4 直接 FIFO 帧结构接收半满操作示意图262图 10-5 IRQ 中断输出示意图264图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图(重传超时,重传次数为 2)266图 10-11 PRX 自动重收中断示意图267图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 图 | 5-48  | I2C 时钟线下拉等待波形示意图                           | 218 |

| 図 6-1 RF 收发器状态控制示意图253図 6-2 芯片上电进入发送模式示意图255図 6-3 芯片上电进入接收模式示意图255図 7-1 增强型帧结构示意图256図 7-2 直接 FIFO 帧结构示意图257図 8-1 4路 PIPE 通讯示意图258図 10-1 FIFO 控制示意图260図 10-2 两种帧结构模式下 FIFO 结构261図 10-3 直接 FIFO 帧结构接收半满操作示意图262図 10-4 直接 FIFO 帧结构接收半满操作示意图262図 10-5 IRQ 中断输出示意图264図 10-6 ACK 不使能情况中断示意图265図 10-7 ACK 使能正常通讯中断示意图265図 10-8 PTX 自动重传情况 1 中断示意图265図 10-9 PTX 自动重传情况 2 中断示意图266図 10-10 PTX 自动重传情况 3 中断示意图(重传超时,重传次数为 2)266図 10-11 PRX 自动重收中断示意图266図 10-12 ACK 使能情况下 NOACK 功能中断示意图268図 10-13 直接 FIFO 帧结构中断示意图268図 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 图 | 5-49  | ADC 内部结构图                                  | 227 |

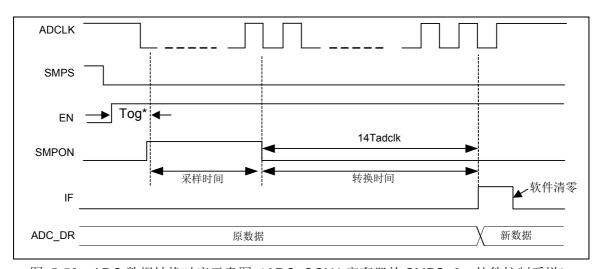

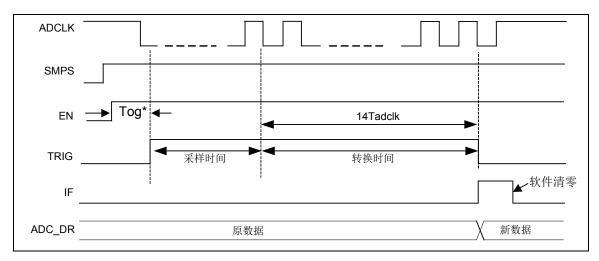

| 図 6-2 芯片上电进入发送模式示意图255図 6-3 芯片上电进入接收模式示意图255図 7-1 增强型帧结构示意图256図 7-2 直接 FIFO 帧结构示意图257図 8-1 4路 PIPE 通讯示意图258図 10-1 FIFO 控制示意图260図 10-2 两种帧结构模式下 FIFO 结构261図 10-3 直接 FIFO 帧结构发送半空操作示意图262図 10-4 直接 FIFO 帧结构接收半满操作示意图262図 10-5 IRQ 中断输出示意图264図 10-6 ACK 不使能情况中断示意图265図 10-7 ACK 使能正常通讯中断示意图265図 10-9 PTX 自动重传情况 1 中断示意图265図 10-10 PTX 自动重传情况 2 中断示意图266図 10-11 PRX 自动重传情况 3 中断示意图266図 10-12 ACK 使能情况下 NOACK 功能中断示意图267図 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 图 | 5-51  | ADC 数据转换时序示意图(ADC_CON1 寄存器的 SMPS=1,硬件控制采样) | 229 |

| 图 6-3 芯片上电进入接收模式示意图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 图 | 6-1   | RF 收发器状态控制示意图                              | 253 |

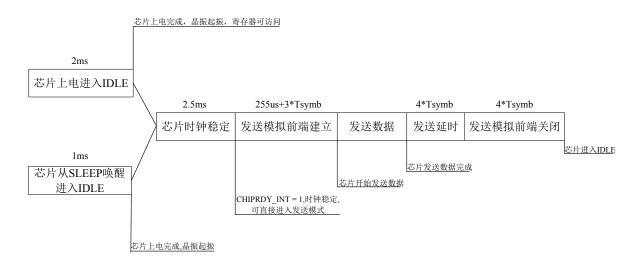

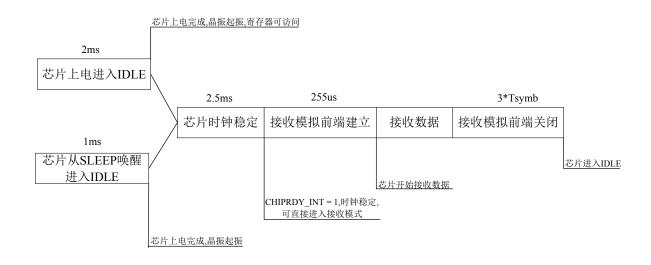

| 图 7-1 增强型帧结构示意图256图 7-2 直接 FIFO 帧结构示意图257图 8-1 4路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图260图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构发送半空操作示意图262图 10-4 直接 FIFO 帧结构接收半满操作示意图262图 10-5 IRQ 中断输出示意图264图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-8 PTX 自动重传情况 1 中断示意图265图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图(重传超时,重传次数为 2)266图 10-11 PRX 自动重使情况下 NOACK 功能中断示意图267图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 图 | 6-2   | 芯片上电进入发送模式示意图                              | 255 |

| 图 7-2 直接 FIFO 帧结构示意图 257 图 8-1 4 路 PIPE 通讯示意图 258 图 10-1 FIFO 控制示意图 260 图 10-2 两种帧结构模式下 FIFO 结构 261 图 10-3 直接 FIFO 帧结构发送半空操作示意图 262 图 10-4 直接 FIFO 帧结构接收半满操作示意图 262 图 10-5 IRQ 中断输出示意图 264 图 10-6 ACK 不使能情况中断示意图 265 图 10-7 ACK 使能正常通讯中断示意图 265 图 10-17 ACK 使的正常通讯中断示意图 265 图 10-18 PTX 自动重传情况 1 中断示意图 266 图 10-19 PTX 自动重传情况 2 中断示意图 266 图 10-10 PTX 自动重传情况 3 中断示意图 266 图 10-11 PRX 自动重传情况 3 中断示意图 266 图 10-12 ACK 使能情况下 NOACK 功能中断示意图 268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 图 | 6-3   | 芯片上电进入接收模式示意图                              | 255 |

| 图 8-1 4路 PIPE 通讯示意图258图 10-1 FIFO 控制示意图260图 10-2 两种帧结构模式下 FIFO 结构261图 10-3 直接 FIFO 帧结构发送半空操作示意图262图 10-4 直接 FIFO 帧结构接收半满操作示意图262图 10-5 IRQ 中断输出示意图264图 10-6 ACK 不使能情况中断示意图265图 10-7 ACK 使能正常通讯中断示意图265图 10-8 PTX 自动重传情况 1 中断示意图266图 10-9 PTX 自动重传情况 2 中断示意图266图 10-10 PTX 自动重传情况 3 中断示意图(重传超时,重传次数为 2)266图 10-11 PRX 自动重收中断示意图267图 10-12 ACK 使能情况下 NOACK 功能中断示意图268图 10-13 直接 FIFO 帧结构中断示意图268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 图 | 7-1   | 增强型帧结构示意图                                  | 256 |

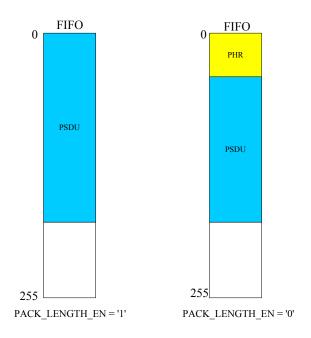

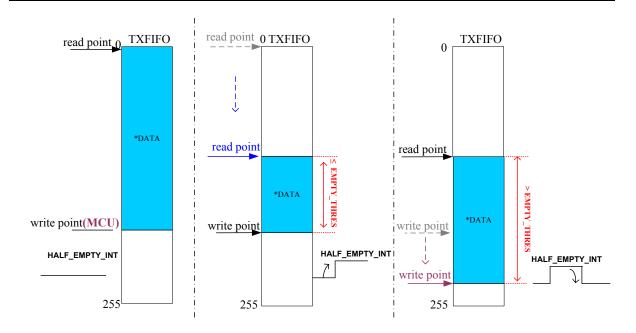

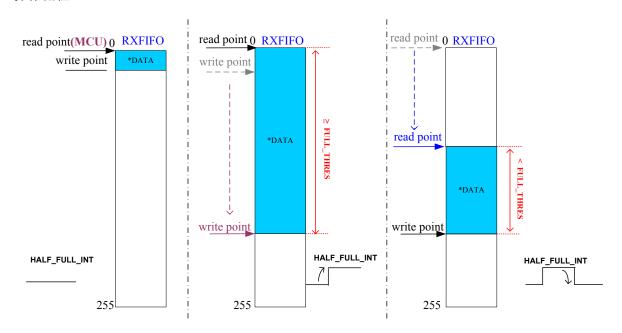

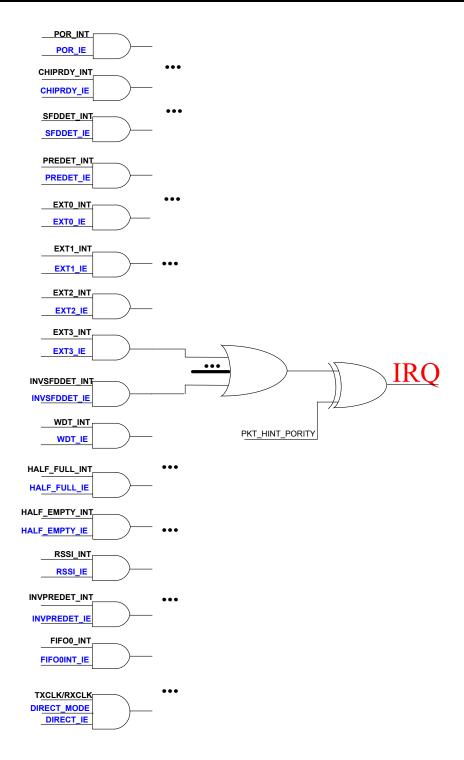

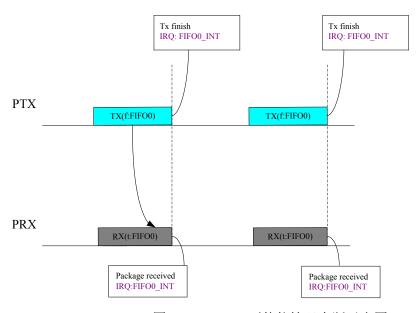

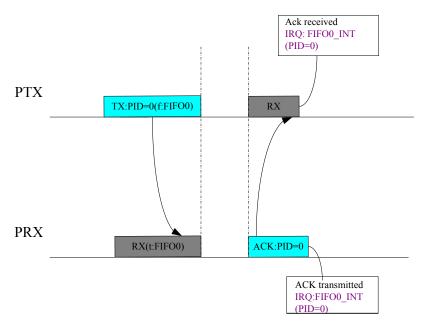

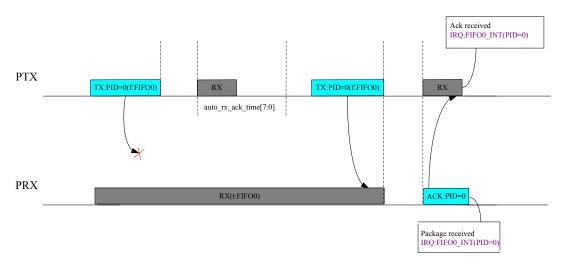

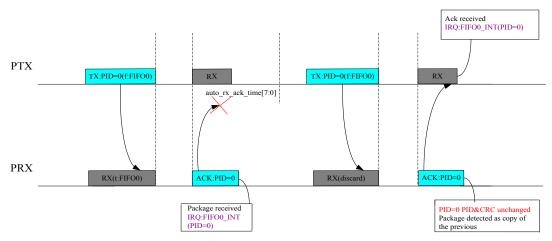

| 图 10-1 FIFO 控制示意图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 图 | 7-2   | 直接 FIFO 帧结构示意图                             | 257 |